Žabky v Digitální Elektroniky

V tomto článku, pojďme se dozvědět se o různé typy žabky používané v digitální elektroniky.

Základní Žabky v Digitální Elektronika

Tento článek se zabývá základní flip flop obvody jako S-R klopný obvod, J-K Flip-Flop, D-Flip Flop a T Flip Flop spolu s pravdivostní tabulky a jejich odpovídající obvodu symboly.

než se pustíte do tématu, je důležité, abyste získali znalosti o jeho základech. Kliknutím na níže uvedené odkazy získáte další informace.

podívejte se: booleovská logika

podívejte se: logické brány

podívejte se: polovina zmije a plná zmije

žabky jsou ve skutečnosti aplikací logických hradel. Pomocí booleovské logiky můžete s nimi vytvořit paměť. Žabky lze také považovat za nejzákladnější myšlenku paměti s náhodným přístupem . Když jim bude dána určitá vstupní hodnota, budou zapamatovány a provedeny, pokud jsou logické brány navrženy správně. Vyšší aplikace žabek je užitečná při navrhování lepších elektronických obvodů.

nejčastěji používaná aplikace žabek je při implementaci zpětnovazebního obvodu. Protože se paměť spoléhá na koncept zpětné vazby, lze k jejímu návrhu použít žabky.

v elektronických obvodech se používají hlavně čtyři typy žabek. Jsou

- základní Flip Flop nebo S-R Flip Flop

- Zpoždění Flip Flop

- J-K Flip Flop

- T Flip Flop

S-R Flip Flop

SET-RESET flip flop je navržen tak, s pomocí dvou ANI vrata a také dvěma branami NAND. Tyto žabky se také nazývají západka S-R.

-

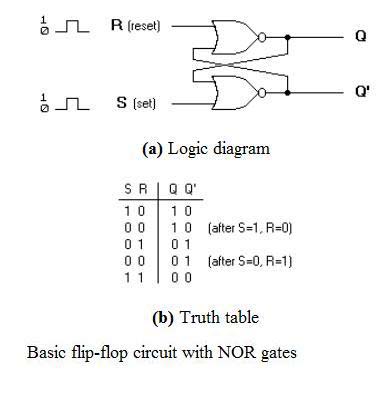

S-R Flip Flop pomocí nor Gate

konstrukce takového flip flopu zahrnuje dva vstupy, nazývané SET a RESET . K dispozici jsou také dva výstupy, Q A Q‘. Tabulka diagramu a pravdy je uvedena níže.

Z diagramu je zřejmé, že flip flop má především čtyři státy. Jsou

S=1, R=0-Q=1, Q ‚ =0

tento stav se také nazývá stav sady.

S=0, R=1-Q=0, Q ‚ =1

tento stav se nazývá stav resetování.

V obou států můžete vidět, že výstupy jsou jen komplimenty navzájem a že hodnota Q následuje hodnota.

S=0, R=0—Q & Q‘ = Pamatovat,

Pokud se obě hodnoty S a R se přepne na 0, obvod si pamatuje hodnotu R a v jejich předchozí stav.

S=1, R=1-Q=0, Q ‚=0

Toto je neplatný stav, protože hodnoty Q i Q ‚ jsou 0. Mají být navzájem komplimenty. Obvykle je třeba se tomuto stavu vyhnout.

-

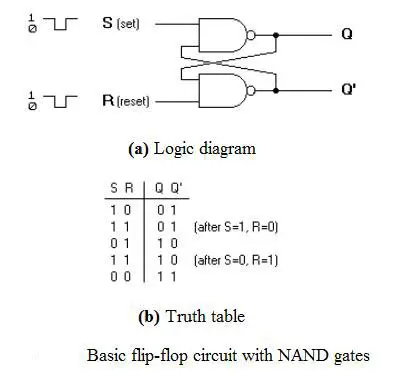

S-R Flip Flop pomocí brány NAND

obvod s-R flip flop pomocí NAND Gate a jeho pravda tabulka je uvedena níže.

stejně jako flip flop NOR Gate S-R má tento také čtyři stavy. Jsou

S=1, R=0-Q=0, Q ‚ =1

tento stav se také nazývá stav sady.

S=0, R=1-Q=1, Q ‚ =0

tento stav se nazývá stav resetování.

V obou států můžete vidět, že výstupy jsou jen komplimenty navzájem a že hodnota Q navazuje na kompliment hodnotu.

S=0, R=0—Q=1, & Q‘ =1

Pokud se obě hodnoty S a R se přepne na 0 je neplatný stát, protože hodnoty Q a Q‘ 1. Mají být navzájem komplimenty. Obvykle je třeba se tomuto stavu vyhnout.

S=1, R=1—Q & Q’= Pamatovat,

Pokud se obě hodnoty S a R se přepne na 1, pak obvod si pamatuje hodnotu R a v jejich předchozí stav.

-

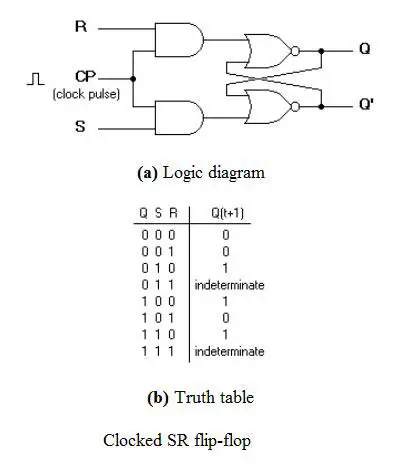

Taktovaný S-R Flip Flop

To je také nazýváno Bránou S-R flip flop.

problémy s žabkami S-R pomocí brány NOR a NAND jsou neplatným stavem. Tento problém lze překonat pomocí bistable SR flip-flopu, který může měnit výstupy, když jsou splněny určité neplatné stavy, bez ohledu na stav sady nebo Resetovacích vstupů. Za tímto účelem je taktovaný flip flop s-R navržen přidáním dvou a bran do základního flip flopu NOR Gate. Schéma zapojení a tabulka pravdy jsou uvedeny níže.

hodiny pulsu je dána vstupy A Brány. Když je hodnota hodinového pulsu „0“, výstupy obou hradel a hradel zůstávají „0“. Jakmile puls je dána hodnota CP otočí ‚1‘. To dělá hodnoty na S A R projít nor Gate flip flop. Ale když se hodnoty obou hodnot S A R změní na „1“, vysoká hodnota CP způsobí, že se obě na krátkou chvíli změní na „0“. Jakmile je pulz odstraněn, stav flip flop se stává přechodným. Může tedy být způsoben jeden ze dvou stavů a záleží na tom, zda vstup set nebo reset flip-flopu zůstává o “ 1 „delší než přechod na“ 0 “ na konci impulsu. Neplatné stavy tak mohou být odstraněny.

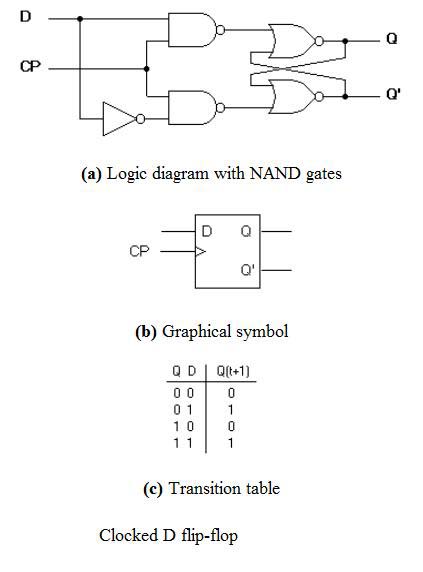

D Flip Flop

schéma zapojení a tabulka pravdy jsou uvedeny níže.

D flip flop je vlastně mírnou úpravu výše vysvětlil, taktovaný SR flip-flop. Z obrázku je vidět, že vstup D je připojen ke vstupu S a doplněk vstupu D je připojen ke vstupu R. Vstup D je předán flip flopu, když je hodnota CP ‚1‘. Když je CP vysoká, flip flop se přesune do nastaveného stavu. Pokud je „0“, flip flop se přepne do jasného stavu.

Chcete-li se dozvědět více o spuštění flip flopu, klikněte na odkaz níže.

PODÍVEJTE se : zahájení ŽABKY

PODÍVEJTE se : MASTER-SLAVE FLIP FLOP OBVODU

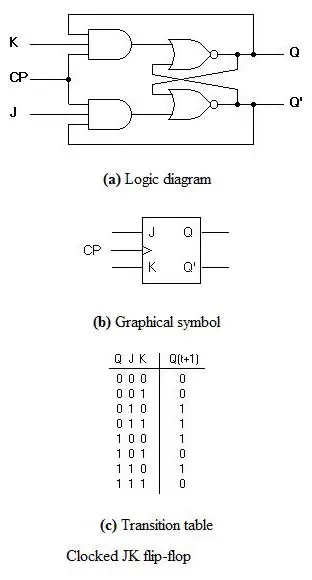

J-K Flip Flop

schéma a pravda-tabulka J-K flip flop je uvedeno níže.

j-k flip flop lze také definovat jako modifikaci s-R flip flop. Jediným rozdílem je, že mezilehlý stav je rafinovanější a přesnější než u flip flopu S-R.

chování vstupů J A K je stejné jako vstupy S A R flip flopu S-R. Písmeno J znamená SET a písmeno K znamená CLEAR.

když mají oba vstupy J A K vysoký stav, přepne se flip-flop do stavu komplementu. Takže pro hodnotu Q = 1 se přepne na Q=0 a pro hodnotu Q = 0 se přepne na Q=1.

obvod obsahuje dvě 3-vstupní a hradla. Výstup Q flip flopu je vrácen zpět jako zpětná vazba na vstup a spolu s dalšími vstupy, jako je k a hodinový puls . Pokud je tedy hodnota CP ‚1‘, flip flop dostane jasný signál as podmínkou, že hodnota Q byla dříve 1. Podobně výstup Q‘ flip flop je uveden jako zpětná vazba na vstup A spolu s dalšími vstupy, jako J a hodiny puls . Výstup se tedy nastaví, když hodnota CP je 1, pouze pokud hodnota Q ‚ byla dříve 1.

výstup může být opakován v přechody, jakmile byly pochválil pro J=K=1 z důvodu zpětné vazby v JK flip-flop. Tomu lze zabránit nastavením doby trvání menší než zpoždění šíření přes flip-flop. Omezení šířky impulsu lze odstranit pomocí konstrukce master-slave nebo edge-triggered.

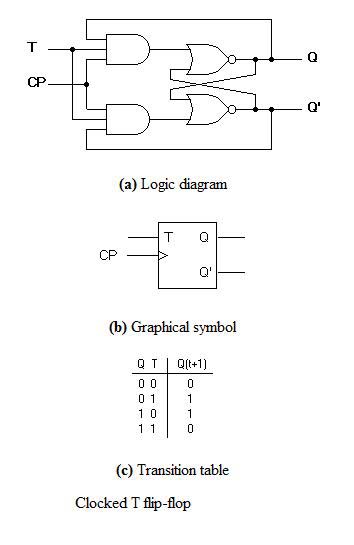

t Flip Flop

Toto je mnohem jednodušší verze J-K flip flop. Oba vstupy J A K jsou spojeny dohromady, a proto se také nazývají jediný vstup J-K flip flop. Když je hodinový puls dán klopnému flopu, výstup se začne přepínat. Zde lze také odstranit omezení šířky impulsu pomocí konstrukce master-slave nebo edge-triggered. Podívejte se na tabulku obvodu a pravdy níže.