Flip Flops i Digital elektronik

i denne artikel lærer vi om forskellige typer flip flops, der bruges i digital elektronik.

grundlæggende Flip Flops i Digital elektronik

denne artikel omhandler de grundlæggende flip flop kredsløb som S-R Flip Flop, J-K Flip Flop, D Flip Flop og T Flip Flop sammen med sandhedstabeller og deres tilsvarende kredsløbssymboler.

før du går til emnet er det vigtigt, at du får kendskab til dets grundlæggende. Klik på nedenstående links for mere information.

tag et kig : boolsk logik

tag et kig : logiske porte

tag et kig : halv ADDER og fuld ADDER

Flip flops er faktisk en anvendelse af logiske porte. Ved hjælp af boolsk logik kan du oprette hukommelse med dem. Flip flops kan også betragtes som den mest grundlæggende ide om en tilfældig adgangshukommelse . Når en bestemt inputværdi er givet til dem, vil de blive husket og udført, hvis de logiske porte er designet korrekt. En højere anvendelse af flip flops er nyttig til at designe bedre elektroniske kredsløb.

den mest anvendte anvendelse af flip flops er i implementeringen af et feedback kredsløb. Da en hukommelse er afhængig af feedbackkonceptet, kan flip flops bruges til at designe det.

der er hovedsageligt fire typer flip flops, der bruges i elektroniske kredsløb. De er

- den grundlæggende Flip Flop eller S-R Flip Flop

- Delay Flip Flop

- J-K Flip Flop

- T Flip Flop

S-R Flip Flop

set-RESET flip flop er designet til ved hjælp af to nor porte og også to NAND porte. Disse flip flops kaldes også S-R låsen.

-

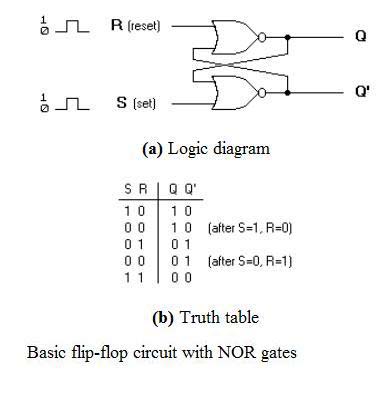

SR Flip Flop ved hjælp af NOR Gate

udformningen af en sådan flip flop omfatter to indgange, kaldet SET og RESET . Der er også to udgange, K og K’. Diagrammet og sandhedstabellen er vist nedenfor.

fra diagrammet er det tydeligt, at flip flop hovedsageligt har fire tilstande. De er

S=1, R=0—K=1, K’=0

denne tilstand kaldes også den indstillede tilstand.

S=0, R=1—K=0, K’=1

denne tilstand er kendt som NULSTILLINGSTILSTAND.

i begge stater kan du se, at output kun er komplimenter af hinanden, og at værdien af K følger værdien af S.

S=0, R=0—K & K’ = husk

hvis både værdierne for S og R skiftes til 0, husker kredsløbet værdien af S og R i deres tidligere tilstand.

S=1, R=1—K=0, K’=0

dette er en ugyldig tilstand, fordi værdierne for både K og K’ er 0. De formodes at være komplimenter af hinanden. Normalt skal denne tilstand undgås.

-

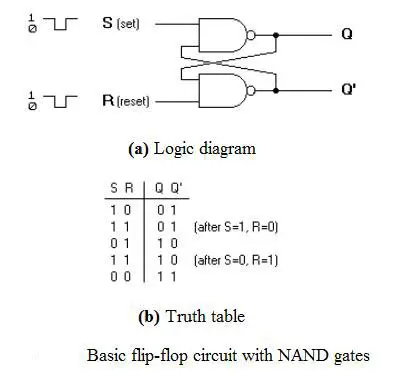

SR Flip Flop ved hjælp af NAND Gate

kredsløbet af S – R flip flop hjælp NAND Gate og dens sandhed tabel er vist nedenfor.

ligesom NOR Gate s-r flip flop har denne også fire tilstande. De er

S=1, R=0—K=0, K’=1

denne tilstand kaldes også den indstillede tilstand.

S=0, R=1—K=1, K’=0

denne tilstand er kendt som NULSTILLINGSTILSTAND.

i begge stater kan du se, at output kun er komplimenter af hinanden, og at værdien af K følger komplimentværdien af S.

S=0, R=0—K=1, & K’ =1

hvis både værdierne for S og R skiftes til 0, er det en ugyldig tilstand, fordi værdierne for både K og K’ er 1. De formodes at være komplimenter af hinanden. Normalt skal denne tilstand undgås.

S=1, R=1—K & K’= husk

hvis både værdierne for S og R skiftes til 1, husker kredsløbet værdien af S og R i deres tidligere tilstand.

-

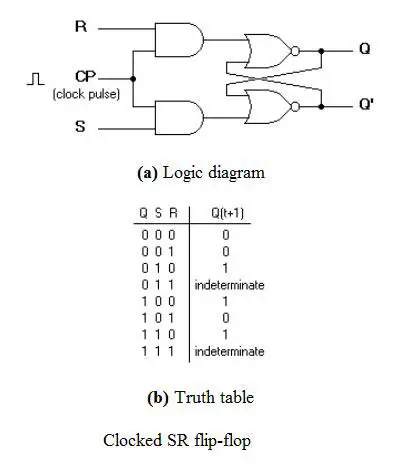

clocket S-R Flip Flop

det kaldes også en Gated s-r flip flop.

problemerne med S-R flip flops ved hjælp af NOR og NAND gate er den ugyldige tilstand. Dette problem kan overvindes ved hjælp af en bistabel SR-flip-flop, der kan ændre output, når visse ugyldige tilstande er opfyldt, uanset betingelsen for enten Sættet eller Nulstillingsindgangene. Til dette er en clocket s-r flip flop designet ved at tilføje to og porte til en grundlæggende NOR Gate flip flop. Kredsløbsdiagrammet og sandhedstabellen er vist nedenfor.

en urpuls gives til indgangene på AND-porten. Når værdien af urpulsen er ‘0’, forbliver udgangene fra både og porte’0′. Så snart en puls er givet, bliver værdien af CP ‘1’. Dette gør værdierne ved S og R til at passere gennem NOR Gate flip flop. Men når værdierne for både S-og R-værdier bliver ‘1’, får den høje værdi af CP dem begge til at vende sig til ‘0’ i et kort øjeblik. Så snart pulsen er fjernet, bliver flip flop-tilstanden mellemliggende. Således kan en af de to tilstande være forårsaget, og det afhænger af, om den indstillede eller nulstillede indgang på flip-flop forbliver en ‘1’ længere end overgangen til ‘0’ i slutningen af pulsen. Således kan de ugyldige stater elimineres.

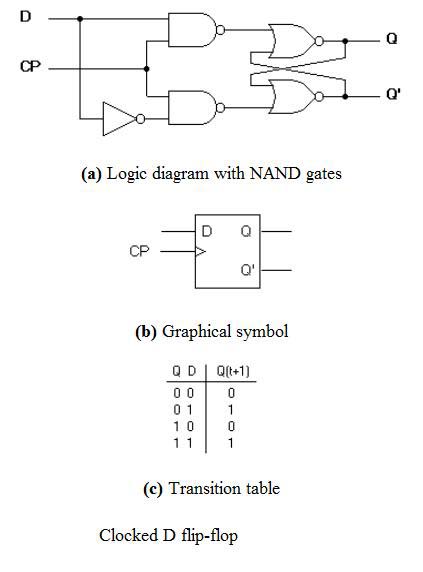

D Flip Flop

kredsløbsdiagrammet og sandhedstabellen er angivet nedenfor.

D flip flop er faktisk en lille ændring af ovenstående forklarede clocket SR flip-flop. Fra figuren kan du se, at d-indgangen er forbundet til s-indgangen, og komplementet til D-indgangen er forbundet til R-indgangen. D-indgangen overføres til flip flop, når værdien af CP er ‘1’. Når CP er høj, flytter flip flop til den indstillede tilstand. Hvis det er’ 0′, skifter flip flop til klar tilstand.

for at vide mere om udløsningen af flip flop klik på linket nedenfor.

tag et kig : udløsning af FLIP FLOPS

tag et kig : MASTER-SLAVE FLIP FLOP CIRCUIT

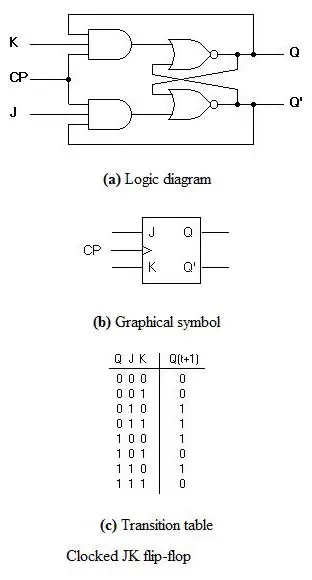

J-K Flip Flop

kredsløbsdiagrammet og sandhedstabellen for en J-K flip flop er vist nedenfor.

en J-K flip flop kan også defineres som en ændring af S-R flip flop. Den eneste forskel er, at mellemtilstanden er mere raffineret og præcis end en S-R flip flop.

opførslen af input J og K er den samme som S-og R-indgangene på S-R flip flop. Bogstavet J står for SET og bogstavet K står for CLEAR.

når både indgangene J og K har en høj tilstand, skifter flip-flop til komplementtilstanden. Så for en værdi på K = 1 skifter den til K=0 og for en værdi på K = 0 skifter den til K=1.

kredsløbet omfatter to 3-input og porte. Output k af flip flop returneres tilbage som en feedback til input af og sammen med andre indgange som K og clock pulse . Så hvis værdien af CP er ‘1’, får flip flop et klart signal og med den betingelse, at værdien af C var tidligere 1. Tilsvarende output k’ af flip flop er givet som en feedback til input af og sammen med andre indgange som J og clock pulse . Så output bliver indstillet, når værdien af CP kun er 1, hvis værdien af K’ var tidligere 1.

udgangen kan gentages i overgange, når de er blevet komplimenteret for J=K=1 på grund af feedbackforbindelsen i JK flip-flop. Dette kan undgås ved at indstille en tidsvarighed, der er mindre end udbredelsesforsinkelsen gennem flip-flop. Begrænsningen på pulsbredden kan elimineres med en master-slave eller kantudløst konstruktion.

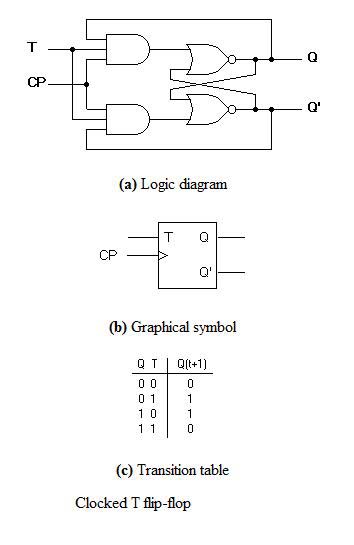

T Flip Flop

dette er en meget enklere version af J-K flip flop. Både J-og K-indgangene er forbundet sammen og kaldes således også en enkelt input J-K flip flop. Når uret puls er givet til flip flop, output begynder at skifte. Her kan også begrænsningen på pulsbredden elimineres med en master-slave eller kantudløst konstruktion. Tag et kig på kredsløbet og sandheden tabellen nedenfor.