Flip flopok a digitális elektronikában

ebben a cikkben megismerjük a digitális elektronikában használt különböző típusú papucsokat.

alapvető Flip flopok a digitális elektronikában

ez a cikk az alapvető flip flop áramkörökkel foglalkozik, mint például az S-R Flip Flop, a J-K Flip Flop, a D Flip Flop és a T Flip Flop, az igazságtáblákkal és a hozzájuk tartozó áramköri szimbólumokkal együtt.

mielőtt a témához lépne, fontos, hogy megismerje annak alapjait. Kattintson az alábbi linkekre további információkért.

vess egy pillantást : logikai logika

vess egy pillantást : logikai kapuk

vess egy pillantást : fél vipera és teljes Vipera

a Flip-flopok valójában a logikai kapuk alkalmazása. A logikai logika segítségével memóriát hozhat létre velük. A papucsok a véletlen hozzáférésű memória legalapvetőbb ötletének is tekinthetők . Ha egy bizonyos bemeneti értéket adnak nekik, akkor emlékezni fognak és végrehajtják őket, ha a logikai kapuk helyesen vannak megtervezve. A papucsok magasabb alkalmazása hasznos a jobb elektronikus áramkörök tervezésében.

a flip-flopok leggyakrabban használt alkalmazása egy visszacsatoló áramkör megvalósítása. Mivel a memória a visszacsatolási koncepcióra támaszkodik, papucsokkal lehet megtervezni.

főleg négyféle papucs létezik, amelyeket elektronikus áramkörökben használnak. Ezek

- az alapvető Flip flop vagy S-R Flip Flop

- késleltetett Flip Flop

- J-K Flip Flop

- T Flip flop

S-R Flip Flop

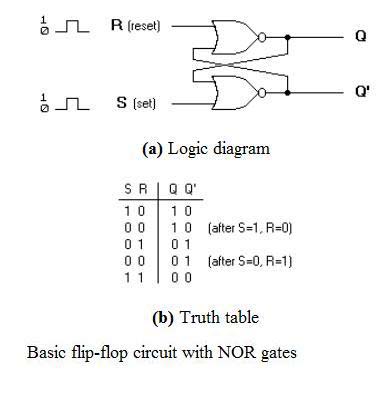

a SET-RESET flopot úgy tervezték, hogy két nor kapu és két NAND kapu segítségével. Ezeket a papucsokat S-R retesznek is nevezik.

-

S-R Flip Flop használata NOR kapu

az ilyen flip flop kialakítása két bemenetet tartalmaz, az úgynevezett SET and RESET . Két kimenet is van, Q és Q’. A diagram és az igazság táblázat az alábbiakban látható.

a diagramból nyilvánvaló, hogy a flip flopnak főleg négy állapota van. Ezek

S=1, R=0—Q=1, Q’=0

ezt az állapotot beállított állapotnak is nevezik.

S=0, R=1—Q=0, Q’=1

ezt az állapotot RESET állapotnak nevezik.

mindkét állapotban látható, hogy a kimenetek csak egymás bókjai, és hogy a Q értéke követi az S értékét.

S=0, R=0—Q & Q’ = Emlékezz

ha mind az S, mind az R értéke 0-ra van kapcsolva, akkor az áramkör megjegyzi az S és R értékét az előző állapotukban.

S=1, R=1—Q=0, Q’=0

ez érvénytelen állapot, mert mind a Q, mind a Q’ értéke 0. Állítólag egymás bókjai. Általában ezt az állapotot el kell kerülni.

-

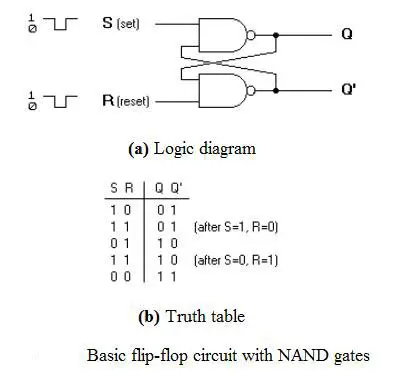

S-R Flip Flop a NAND kapu használatával

az S-R flip flop áramköre a NAND Gate használatával és annak igazságtáblája az alábbiakban látható.

mint a NOR kapu S-R flip flop, ez is négy állam. Ezek

S=1, R=0—Q=0, Q’=1

ezt az állapotot beállított állapotnak is nevezik.

S=0, R=1—Q=1, Q’=0

ezt az állapotot RESET állapotnak nevezik.

mindkét állapotban látható, hogy a kimenetek csak egymás bókjai, és hogy a Q értéke követi az S bók értékét.

S=0, R=0—Q=1, & Q’ =1

ha mind az S, mind az R értéke 0-ra van kapcsolva, akkor érvénytelen állapot, mert mind a Q, mind a Q’ értéke 1. Állítólag egymás bókjai. Általában ezt az állapotot el kell kerülni.

S=1, R=1—Q & Q’= Emlékezz

ha mind az S, mind az R értéke 1-re van kapcsolva, akkor az áramkör megjegyzi az S és R értékét az előző állapotukban.

-

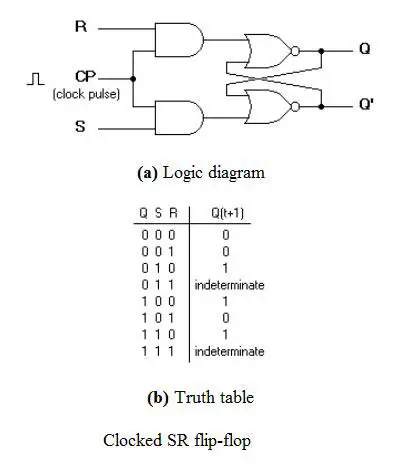

órajelű S-R Flip Flop

úgy is nevezik, egy kapuzott S-R flip flop.

az S-R flip-flopok problémái a NOR és a NAND gate használatával Az érvénytelen állapot. Ez a probléma megoldható egy bistable SR flip-flop használatával, amely megváltoztathatja a kimeneteket, ha bizonyos érvénytelen állapotok teljesülnek, függetlenül a Set vagy a Reset bemenetek állapotától. Ehhez egy órajelű S-R flip flopot úgy terveztek, hogy kettőt és kapukat adnak hozzá egy alap NOR Gate flip flophoz. A kapcsolási rajz és az igazság táblázat az alábbiakban látható.

egy órajel impulzust kap az And Gate bemenetei. Ha az óraimpulzus értéke ‘0’, akkor mind a kapuk, mind a kapuk kimenete’0′ marad. Amint egy impulzus meg van adva, a CP értéke ‘1’ – re fordul. Ez teszi az értékeket S és R, hogy áthaladjon a NOR kapu flip flop. De amikor mind az S, mind az R értékek értéke ‘1’ – re fordul, a CP magas értéke miatt mindkettő rövid pillanatra ‘0’ – ra fordul. Amint az impulzus eltávolításra kerül, a flip flop állapot köztes lesz. Így a két állapot bármelyike kiváltható, és ez attól függ, hogy a flip-flop set vagy reset bemenete ‘1’ marad-e hosszabb ideig, mint az impulzus végén a ‘0’ – ra való átmenet. Így Az érvénytelen állapotok kiküszöbölhetők.

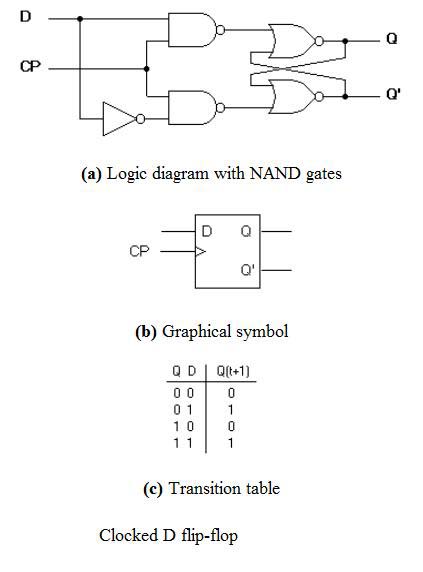

D Flip Flop

a kapcsolási rajz és az igazság táblázat az alábbiakban található.

a D flip flop valójában a fent leírt órajelű SR flip-flop enyhe módosítása. Az ábrán látható, hogy a D bemenet csatlakozik az S bemenethez, a D bemenet kiegészítője pedig az R bemenethez. A D bemenet továbbadódik a flip flopnak, amikor a CP értéke ‘1’. Ha a CP magas, a flip flop a beállított állapotba kerül. Ha ez ‘0’, a flip flop átvált a tiszta állapot.

ha többet szeretne tudni a flip flop indításáról, kattintson az alábbi linkre.

vessen egy pillantást : flip-flopok kiváltása

vessen egy pillantást : MASTER-SLAVE FLIP flop áramkör

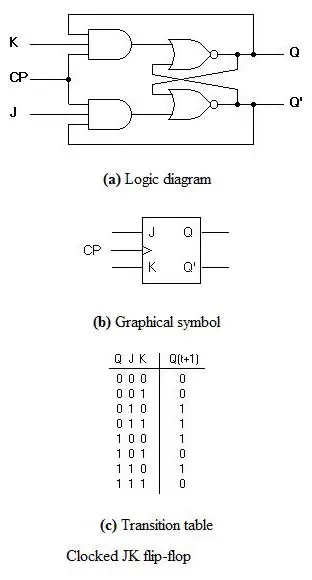

J-K Flip Flop

a J-K flip flop kapcsolási rajza és igazságtáblája az alábbiakban látható.

a J-K flip flop az S-R flip flop módosításának is tekinthető. Az egyetlen különbség az, hogy a köztes állapot kifinomultabb és pontosabb, mint az S-R flip flop.

a J és K bemenetek viselkedése megegyezik az S-R flip flop s és R bemeneteivel. A J betű a SET-et, a K betű pedig a CLEAR-t jelenti.

ha mind a J, mind a K bemenetek magas állapotban vannak, a flip-flop KOMPLEMENT állapotba kapcsol. Tehát Q = 1 érték esetén Q=0 értékre, Q = 0 értékre pedig Q=1 értékre vált.

az áramkör két 3 bemenetet és kaput tartalmaz. A flip flop Q kimenete visszacsatolásként kerül vissza Az and bemenetére, más bemenetekkel együtt, mint például a K és az óra impulzusa . Tehát, ha a CP értéke ‘1’, A flip flop egyértelmű jelet kap azzal a feltétellel, hogy Q értéke korábban 1 volt. Hasonlóképpen a flip flop Q’ kimenete visszacsatolásként jelenik meg az AND bemenetére, más bemenetekkel együtt, mint a J és az óra impulzus . Tehát a kimenet akkor lesz beállítva, ha a CP értéke 1, csak akkor, ha Q’ értéke korábban 1 volt.

a kimenet átmenetben megismételhető, miután a J=K=1-hez gratuláltak a JK flip-flop visszacsatolási kapcsolata miatt. Ez elkerülhető, ha a flip-flopon keresztüli terjedési késleltetésnél kisebb időtartamot állítunk be. Az impulzusszélesség korlátozása kiküszöbölhető master-slave vagy él által kiváltott konstrukcióval.

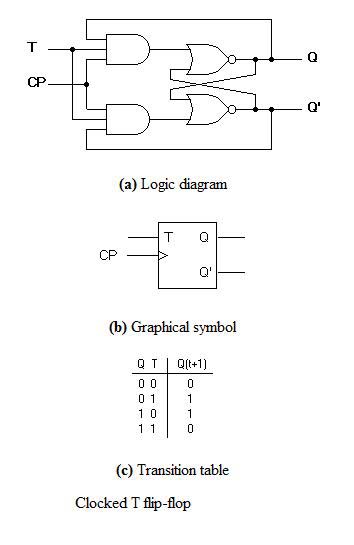

T Flip Flop

ez a J-K flip flop sokkal egyszerűbb változata. Mind a J, mind a K bemenetek össze vannak kötve, így egyetlen bemenetnek is nevezik J-K flip flop. Amikor az óra impulzusát a flip flop adja meg, a kimenet váltogatni kezd. Itt is az impulzusszélesség korlátozása kiküszöbölhető egy master-slave vagy él által kiváltott konstrukcióval. Vessen egy pillantást az alábbi áramköri és igazság táblázatra.