Infradito in elettronica digitale

In questo articolo, impariamo a conoscere diversi tipi di infradito utilizzati nell’elettronica digitale.

Infradito di base nell’elettronica digitale

Questo articolo tratta i circuiti flip flop di base come S-R Flip Flop, J-K Flip Flop, D Flip Flop e T Flip Flop insieme alle tabelle di verità e ai loro corrispondenti simboli del circuito.

Prima di andare all’argomento è importante conoscere le sue basi. Clicca sui link qui sotto per maggiori informazioni.

DAI UN’OCCHIATA : LOGICA BOOLEANA

DAI UN’OCCHIATA : PORTE LOGICHE

DAI UN’OCCHIATA : MEZZA VIPERA E PIENA VIPERA

Infradito sono in realtà un’applicazione di porte logiche. Con l’aiuto della logica booleana puoi creare memoria con loro. Infradito può anche essere considerato come l’idea di base di una memoria ad accesso casuale . Quando viene dato loro un determinato valore di input, verranno ricordati ed eseguiti, se le porte logiche sono progettate correttamente. Una maggiore applicazione di infradito è utile nella progettazione di circuiti elettronici migliori.

L’applicazione più comunemente utilizzata delle infradito è nell’implementazione di un circuito di feedback. Poiché una memoria si basa sul concetto di feedback, le infradito possono essere utilizzate per progettarlo.

Ci sono principalmente quattro tipi di infradito che vengono utilizzati nei circuiti elettronici. Sono

- base Flip Flop S-R Flip Flop

- Ritardo Flip Flop

- J-K Flip-Flop

- T Flip-Flop

S-R Flip Flop

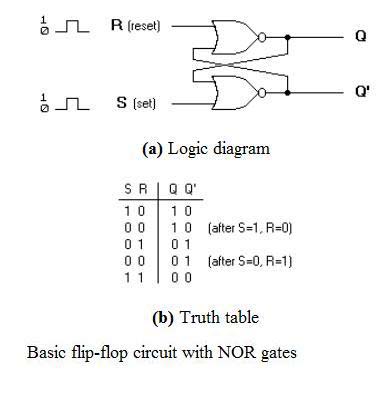

SET-RESET del flip flop è stato progettato con l’aiuto di due NÉ porte e due porte NAND. Queste infradito sono anche chiamate S-R Latch.

-

SR Flip Flop utilizzando NOR Cancello

Il design di un tale flip flop include due ingressi, chiamati SET e RESET . Ci sono anche due uscite, Q e Q’. Il diagramma e la tabella di verità è mostrato di seguito.

Dal diagramma è evidente che il flip flop ha principalmente quattro stati. Sono

S = 1, R=0-Q=1, Q’ = 0

Questo stato è anche chiamato stato IMPOSTATO.

S = 0, R=1-Q=0, Q’ = 1

Questo stato è noto come stato di RESET.

In entrambi gli stati puoi vedere che gli output sono solo complimenti l’uno dell’altro e che il valore di Q segue il valore di S.

S=0, R = 0—Q & Q’ = Ricorda

Se entrambi i valori di S e R sono passati a 0, il circuito ricorda il valore di S e R nel loro stato precedente.

S=1, R=1—Q=0, Q’=0

Questo è uno stato non valido perché i valori di Q e Q’ sono 0. Dovrebbero essere complimenti l’uno dell’altro. Normalmente, questo stato deve essere evitato.

-

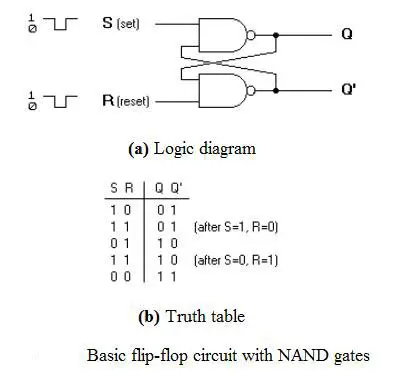

SR Flip Flop utilizzando porta NAND

Il circuito del flip flop SR utilizzando NAND Gate e la sua tabella di verità è mostrato di seguito.

Come il NOR Gate SR flip flop, anche questo ha quattro stati. Sono

S = 1, R=0-Q=0, Q’ = 1

Questo stato è anche chiamato stato IMPOSTATO.

S = 0, R=1-Q=1, Q’ = 0

Questo stato è noto come stato di RESET.

In entrambi gli stati puoi vedere che gli output sono solo complimenti l’uno dell’altro e che il valore di Q segue il valore di complimento di S.

S=0, R=0—Q =1, & Q’ = 1

Se entrambi i valori di S e R vengono commutati su 0, lo stato non è valido perché i valori di Q e Q’ sono 1. Dovrebbero essere complimenti l’uno dell’altro. Normalmente, questo stato deve essere evitato.

S=1, R= 1—Q & Q’ = Ricorda

Se entrambi i valori di S e R sono passati a 1, il circuito ricorda il valore di S e R nel loro stato precedente.

-

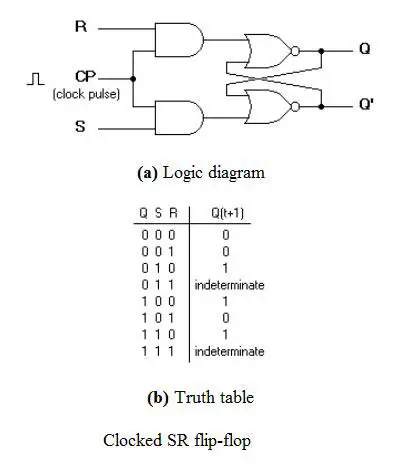

Flip Flop S-R con clock

E ‘ anche chiamato un Gated S-R flip flop.

I problemi con le infradito SR che utilizzano NOR e NAND gate sono lo stato non valido. Questo problema può essere superato utilizzando un flip-flop SR bistabile che può cambiare le uscite quando determinati stati non validi sono soddisfatti, indipendentemente dalle condizioni degli ingressi Set o Reset. Per questo, un flip flop S-R con clock è progettato aggiungendo due porte E ad un flip flop di base NOR Gate. Lo schema elettrico e la tabella di verità sono mostrati di seguito.

Un impulso di clock viene dato agli ingressi del gate AND. Quando il valore dell’impulso di clock è “0”, le uscite di entrambe le porte E rimangono “0”. Non appena viene dato un impulso il valore di CP diventa ‘1’. Questo fa sì che i valori di S e R passino attraverso il flip flop NOR Gate. Ma quando i valori di entrambi i valori S e R diventano “1”, l’ALTO valore di CP fa sì che entrambi si trasformino in ” 0 ” per un breve momento. Non appena l’impulso viene rimosso, lo stato flip flop diventa intermedio. Così uno dei due stati può essere causato, e dipende se l’ingresso set o reset del flip-flop rimane un ‘ 1 ‘più lungo della transizione a’ 0 ‘ alla fine dell’impulso. Così gli stati non validi possono essere eliminati.

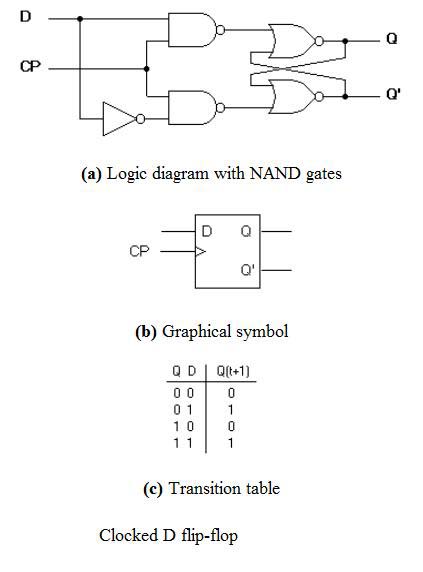

D Flip Flop

Lo schema elettrico e la tabella di verità sono riportati di seguito.

D flip flop è in realtà una leggera modifica del sopra spiegato clock SR flip-flop. Dalla figura si può vedere che l’ingresso D è collegato all’ingresso S e il complemento dell’ingresso D è collegato all’ingresso R. L’input D viene passato al flip flop quando il valore di CP è ‘1’. Quando CP è ALTO, il flip flop si sposta allo stato IMPOSTATO. Se è ‘0’, il flip flop passa allo stato CHIARO.

Per saperne di più sull’attivazione del flip flop clicca sul link sottostante.

DAI UN’OCCHIATA : ATTIVAZIONE DELLE INFRADITO

DAI UN’OCCHIATA : CIRCUITO MASTER-SLAVE FLIP FLOP

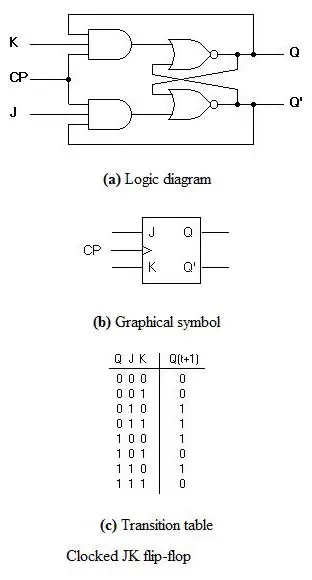

J-K Flip Flop

Lo schema elettrico e la tabella di verità di un flip flop J-K sono mostrati di seguito.

Un flip flop J-K può anche essere definito come una modifica del flip flop S-R. L’unica differenza è che lo stato intermedio è più raffinato e preciso di quello di un flip flop S-R.

Il comportamento degli ingressi J e K è lo stesso degli ingressi S e R del flip flop S-R. La lettera J sta per SET e la lettera K sta per CLEAR.

Quando entrambi gli ingressi J e K hanno uno stato ELEVATO, il flip-flop passa allo stato del complemento. Quindi, per un valore di Q = 1, passa a Q = 0 e per un valore di Q = 0, passa a Q=1.

Il circuito comprende due ingressi E porte a 3 ingressi. L’uscita Q del flip flop viene restituita come feedback all’ingresso del E insieme ad altri ingressi come K e clock pulse . Quindi, se il valore di CP è ‘1’, il flip flop ottiene un segnale CHIARO e con la condizione che il valore di Q fosse precedente 1. Allo stesso modo uscita Q ‘ del flip flop è dato come un feedback per l’ingresso del e insieme ad altri ingressi come J e impulso di clock . Quindi l’output diventa impostato quando il valore di CP è 1 solo se il valore di Q’ era precedente 1.

L’output può essere ripetuto nelle transizioni una volta che sono stati complimentati per J=K=1 a causa della connessione di feedback nel flip-flop JK. Questo può essere evitato impostando una durata di tempo inferiore al ritardo di propagazione attraverso il flip-flop. La restrizione sulla larghezza dell’impulso può essere eliminata con una costruzione master-slave o edge-triggered.

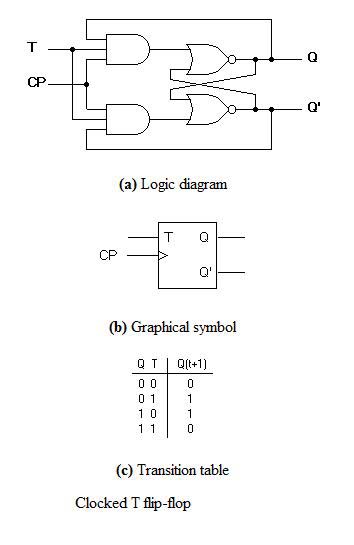

T Flip Flop

Questa è una versione molto più semplice del J-K flip flop. Entrambi gli ingressi J e K sono collegati tra loro e quindi sono anche chiamati un singolo ingresso J-K flip flop. Quando l’impulso di clock viene dato al flip flop, l’uscita inizia a passare. Qui anche la restrizione sulla larghezza dell’impulso può essere eliminata con una costruzione master-slave o edge-triggered. Date un’occhiata al circuito e la tabella di verità qui sotto.