デジタル電子工学のフリップフロップ

この記事では、デジタル電子機器で使用されるさまざまな種類のフリップフロップについて学びましょう。

デジタルエレクトロニクスの基本的なフリップフロップ

この記事では、s-Rフリップフロップ、J-Kフリップフロップ、Dフリップフロップ、Tフリップフロップのような基本的なフリップフロップ回路を真理値表とそれに対応する回路記号とともに扱います。

トピックに行く前に、その基本についての知識を得ることが重要です。 詳細については、以下のリンクをクリックしてください。

見てみましょう:ブール論理

見てみましょう:論理ゲート

見てみましょう:ハーフ加算器とフル加算器

フリップフロップは、実際には論理ゲート ブール論理の助けを借りて、あなたは彼らと一緒にメモリを作成することができます。 フリップフロップは、ランダムアクセスメモリの最も基本的な考え方と考えることもできます。 特定の入力値が与えられると、論理ゲートが正しく設計されていれば、それらは記憶され、実行されます。 フリップフロップのより高い適用はよりよい電子回路の設計で有用である。

フリップフロップの最も一般的に使用されるアプリケーションは、フィードバック回路の実装です。 メモリはフィードバックの概念に依存するため、フリップフロップを使用して設計することができます。

電子回路で使用されるフリップフロップには、主に四つのタイプがあります。 それらは

- 基本的なフリップフロップまたはS-Rフリップフロップ

- 遅延フリップフロップ

- J-Kフリップフロップ

- Tフリップフロップ

S-Rフリップフロップ

セットリセットフリップフロップが設計されています二つのnorゲートと二つのnandゲートの助けを借りて。 これらのフリップフロップはまたS-Rの掛け金と呼ばれます。

-

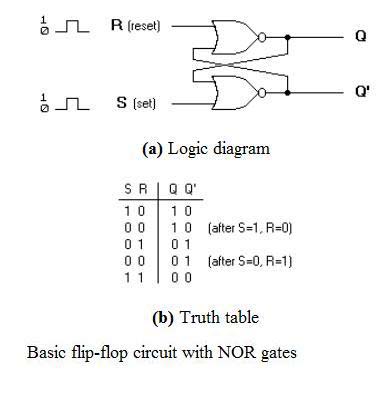

NORゲートを使用したS-Rフリップフロップ

このようなフリップフロップの設計には、セットとリセットと呼ばれる2つの入力が含まれています。 また、2つの出力、QとQ’もあります。 図と真理値表を以下に示します。

図から、フリップフロップは主に四つの状態を有することが明らかである。 それらは

S=1,R=0—Q=1,Q’=0

この状態はセット状態とも呼ばれます。

S=0,R=1—Q=0,Q’=1

この状態をリセット状態といいます。

どちらの状態でも、出力はお互いの単なる賛辞であり、Qの値はSの値に従うことがわかります。

S=0,R=0—Q&Q’=Remember

sとRの両方の値が0に切り替わると、回路は前の状態のSとRの値を記憶します。

S=1,R=1—Q=0,Q’=0

QとQ’の両方の値が0であるため、これは無効な状態です。 彼らはお互いの賛辞であることになっています。 通常、この状態は避ける必要があります。

-

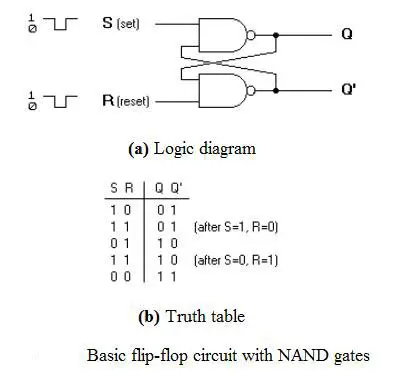

NANDゲートを使用したS-Rフリップフロップ

NANDゲートを使用したS-Rフリップフロップの回路とその真理値表を以下に示します。

NORゲートS-Rフリップフロップと同様に、これも四つの状態を持っています。 それらは

S=1,R=0—Q=0,Q’=1

この状態はセット状態とも呼ばれます。

S=0,R=1—Q=1,Q’=0

この状態をリセット状態といいます。

どちらの状態でも、出力はお互いの単なる補完であり、Qの値はSの補完値に従っていることがわかります。

S=0,R=0—Q=1,&Q’=1

SとRの両方の値を0に切り替えると、QとQ’の両方の値が1であるため無効な状態になります。 彼らはお互いの賛辞であることになっています。 通常、この状態は避ける必要があります。

S=1,R=1—Q&Q’=Remember

sとRの両方の値が1に切り替わると、回路は前の状態のSとRの値を記憶します。

-

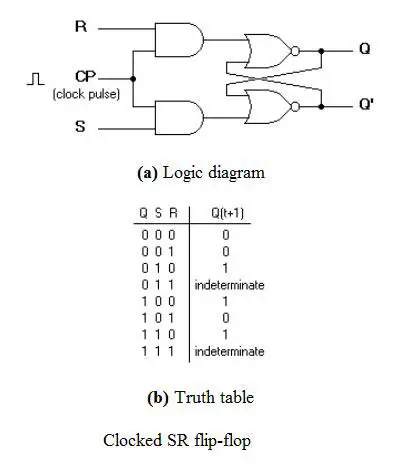

クロックされたS-Rフリップフロップ

それはまたゲートで飾られたS-Rの双安定回路と呼ばれます。

NORとNANDゲートを使用したS-Rフリップフロップの問題は無効な状態です。 この問題は、SetまたはReset入力の条件に関係なく、特定の無効な状態が満たされたときに出力を変更できる双安定SRフリップフロップを使用することに このために、クロックされたS-Rフリップフロップは、基本的なNORゲートフリップフロップに二つのANDゲートを追加することによっ 回路図と真理値表を以下に示します。

ANDゲートの入力にクロックパルスが与えられます。 クロックパルスの値が’0’の場合、ANDゲートの両方の出力は’0’のままになります。 パルスが与えられるとすぐにCPの値は’1’になります。 これにより、SとRの値がNORゲートフリップフロップを通過します。 しかし、S値とR値の両方の値が’1’になると、CPの高い値により、両方が短い間’0’に変わります。 パルスが除去されるとすぐに、フリップフロップ状態は中間になります。 したがって、二つの状態のいずれかが引き起こされる可能性があり、それはフリップフロップのセットまたはリセット入力がパルスの終わりに’0’への遷移よりも長い’1’のままであるかどうかに依存する。 したがって、無効な状態を排除することができます。

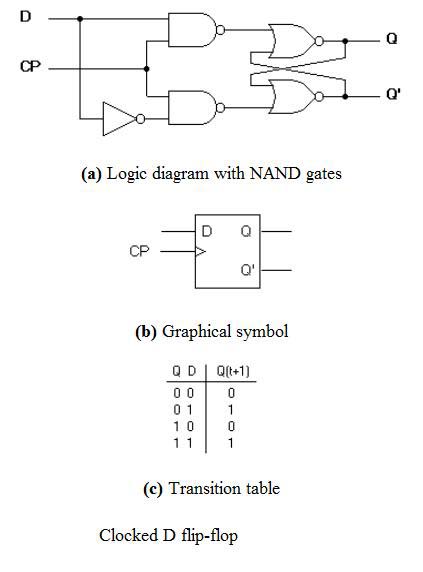

Dフリップフロップ

回路図と真理値表を以下に示します。

Dフリップフロップは、実際には上記で説明したクロックSRフリップフロップのわずかな変更です。 図から、D入力がS入力に接続され、D入力の補数がR入力に接続されていることがわかります。 D入力は、CPの値が’1’のときにフリップフロップに渡されます。 CPがハイのとき、フリップフロップはセット状態に移動します。 これが’0’の場合、フリップフロップはクリア状態に切り替わります。

フリップフロップのトリガーについての詳細を知るには、以下のリンクをクリックしてください。

見てみましょう:フリップフロップのトリガ

見てみましょう:マスター-スレーブフリップフロップ回路

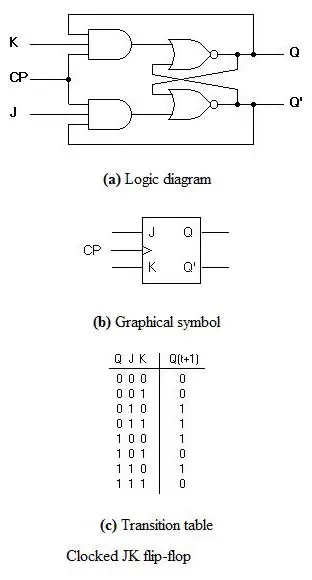

J-Kフリップフロップ

J-Kフリップフロップの回路図と真理値表を以下に示します。

J-Kフリップフロップは、S-Rフリップフロップの変更として定義することもできます。 唯一の違いは、中間状態がS-Rフリップフロップのそれよりも洗練され、正確であることです。

入力JおよびKの動作は、S-RフリップフロップのSおよびR入力と同じです。 文字Jはセットを表し、文字Kはクリアを表します。

入力JとKの両方がハイ状態のとき、フリップフロップは補数状態に切り替わります。 したがって、Q=1の値の場合はQ=0に切り替わり、Q=0の値の場合はQ=1に切り替わります。

回路には2つの3入力ANDゲートが含まれています。 フリップフロップの出力Qは、Kやクロックパルスなどの他の入力とともに、ANDの入力へのフィードバックとして返されます。 したがって、CPの値が’1’の場合、フリップフロップは明確な信号を取得し、Qの値が以前の1であることを条件とします。 同様に、フリップフロップの出力Q’は、Jやクロックパルスのような他の入力とともに、ANDの入力へのフィードバックとして与えられます。 したがって、Q’の値が1より前の場合にのみ、CPの値が1のときに出力が設定されます。

出力は、JKフリップフロップのフィードバック接続のために、J=K=1に対して補完されると、遷移で繰り返される可能性があります。 これは、フリップフロップを介した伝搬遅延よりも短い時間を設定することによって回避することができます。 脈拍幅の制限はマスタースレーブか端誘発された構造と除去することができる。

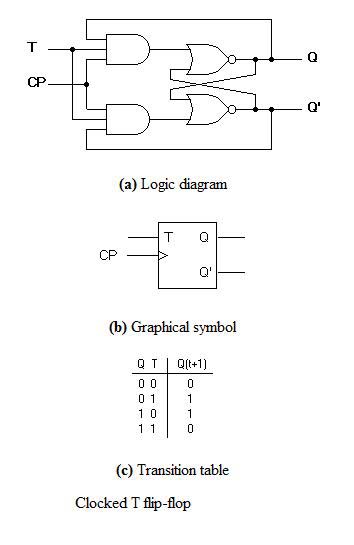

Tフリップフロップ

これはJ-Kフリップフロップのはるかに簡単なバージョンです。 J入力とK入力の両方が一緒に接続されているため、単一入力J-Kフリップフロップとも呼ばれます。 フリップフロップにクロックパルスが与えられると、出力はトグルを開始します。 ここにまた脈拍幅の制限はマスタースレーブか端誘発された構造と除去することができる。 以下の回路と真理値表を見てみましょう。