Flip Flops I Digital Elektronikk

i denne artikkelen, la oss lære om ulike typer flip flops som brukes i digital elektronikk.

Grunnleggende Flip Flops I Digital Elektronikk

denne artikkelen omhandler de grunnleggende flip flop kretser som S-R Flip Flop, Jk Flip Flop, D Flip Flop, Og T Flip Flop sammen med sannhet tabeller og deres tilsvarende krets symboler.

før du går til emnet er det viktig at du får kunnskap om det grunnleggende. Klikk på linkene nedenfor for mer informasjon.

TA EN TITT : BOOLSK LOGIKK

TA EN TITT : LOGISKE PORTER

TA EN TITT : HALV ADDER og FULL ADDER

Flip flops er faktisk en anvendelse av logiske porter. Med Hjelp Av Boolsk logikk kan du lage minne med dem. Flip flops kan også betraktes som Den mest grunnleggende ideen Om Et Tilfeldig Tilgangsminne . Når en bestemt inngangsverdi er gitt til dem, blir de husket og utført, hvis logikkportene er utformet riktig. En høyere anvendelse av flip flops er nyttig i å designe bedre elektroniske kretser.

den mest brukte applikasjonen av flip flops er i implementeringen av en tilbakemeldingskrets. Som et minne er avhengig av tilbakemeldingskonseptet, kan flip flops brukes til å designe det.

det er hovedsakelig fire typer flip flops som brukes i elektroniske kretser. De er

- den grunnleggende Flip Flop eller S-R Flip Flop

- Delay Flip Flop

- J-K Flip Flop

- T Flip Flop

S-R Flip Flop

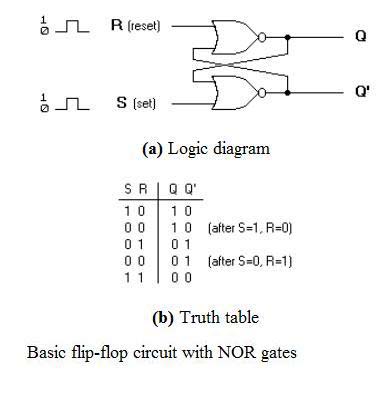

SET-RESET flip flop er designet MED hjelp AV TO eller porter og også to nand-porter. Disse flip flops er også kalt S-R Latch.

-

S – R Flip Flop bruker Nor Gate

utformingen av en slik flip flop inkluderer to innganger, kalt SETTET og RESET . Det er også to utganger, Q Og Q’. Diagrammet og sannhetstabellen er vist nedenfor.

fra diagrammet er det tydelig at flip flop har hovedsakelig fire stater. De er

S=1, R=0—Q=1, Q’=0

DENNE tilstanden kalles OGSÅ SETTTILSTANDEN.

S=0, R=1—Q=0, Q’=1

DENNE tilstanden kalles TILBAKESTILLINGSTILSTANDEN.

i begge statene kan du se at utgangene bare er komplimenter av hverandre, og at verdien Av Q følger verdien Av S.

S=0, R=0-Q & Q ‘ = Husk

hvis begge verdiene Til S Og R er byttet til 0, husker kretsen verdien Av S og R i sin tidligere tilstand.

S=1, R=1—Q=0, Q’=0

dette er en ugyldig tilstand fordi verdiene Til Både Q og Q ‘ er 0. De er ment å være komplimenter av hverandre. Normalt må denne tilstanden unngås.

-

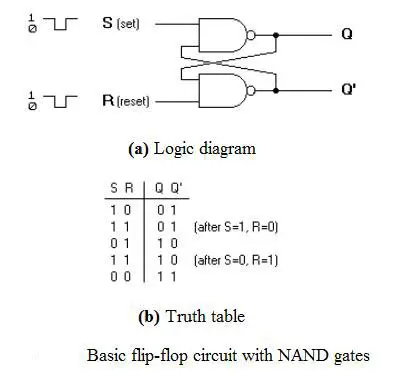

S – R Flip Flop ved HJELP AV NAND Gate

kretsen Av s-R flip flop ved HJELP AV NAND Gate og dens sannhet tabellen er vist nedenfor.

Som NOR Gate S-R flip flop, denne har også fire stater. De er

S=1, R=0—Q=0, Q’=1

DENNE tilstanden kalles OGSÅ SETTTILSTANDEN.

S=0, R=1-Q=1, Q’ = 0

DENNE tilstanden kalles TILBAKESTILLINGSTILSTANDEN.

i begge statene kan du se at utgangene bare er komplimenter av hverandre, og at verdien Av Q følger komplimenteringsverdien Til S.

S=0, R=0-Q=1, & Q’ =1

hvis begge verdiene Til S og R er byttet til 0, er det en ugyldig tilstand fordi verdiene til Både Q Og Q ‘ er 1. De er ment å være komplimenter av hverandre. Normalt må denne tilstanden unngås.

S=1, R=1-Q & Q’ = Husk

hvis begge verdiene Til S Og R er byttet til 1, husker kretsen verdien Av S og R i sin tidligere tilstand.

-

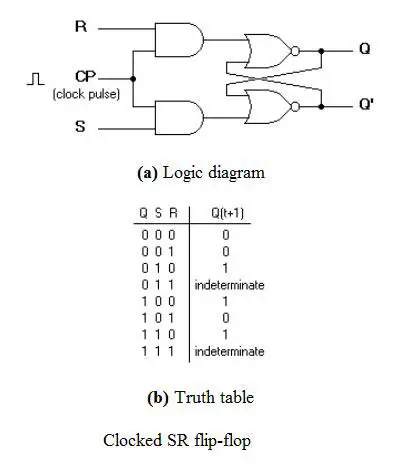

Klokket S-R Flip Flop

Det kalles også En Gated s-r flip flop.

problemene Med S-R flip flops ved HJELP AV NOR og nand gate er ugyldig tilstand. Dette problemet kan løses ved å bruke en bistable sr flip-flop som kan endre utganger når visse ugyldige tilstander er oppfylt, uavhengig av tilstanden Til Enten Settet eller Tilbakestillingsinngangene. For dette er en klokket S-R flip flop designet ved å legge to og porter til en grunnleggende Nor Gate flip flop. Kretsdiagrammet og sannhetstabellen er vist nedenfor.

en klokkepuls er gitt til inngangene TIL Og Gate. Når verdien av klokkepulsen er ‘0’, forblir utgangene til BÅDE Og-Portene ‘0’. Så snart en puls er gitt, blir VERDIEN AV CP ‘1’. Dette gjør verdiene På S Og R for å passere GJENNOM nor Gate flip flop. Men når verdiene for Både s og R verdier slå ‘1’, DEN HØYE verdien AV CP fører begge til å slå til ‘ 0 ‘ for en kort stund. Så snart pulsen er fjernet, blir flip flop-tilstanden mellomliggende. Dermed kan en av de to tilstandene forårsakes, og det avhenger av om settet eller tilbakestillingsinngangen til flip-floppen forblir en ‘ 1 ‘lenger enn overgangen til’ 0 ‘ på slutten av pulsen. Dermed kan de ugyldige statene elimineres.

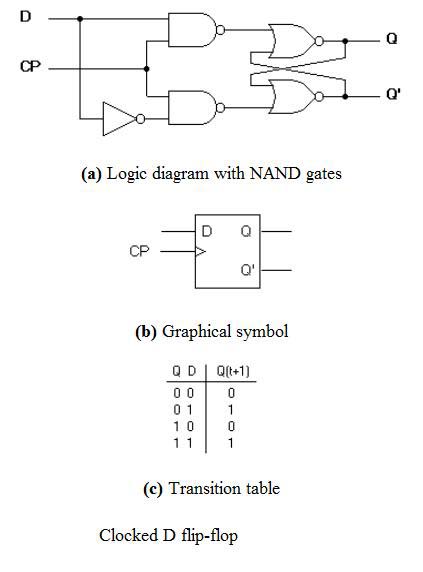

D Flip Flop

kretsdiagrammet og sannhetstabellen er gitt nedenfor.

D flip flop er faktisk en liten modifikasjon av ovennevnte forklart klokket sr flip-flop. Fra figuren kan du se At d-inngangen er koblet Til s-inngangen og komplementet Til D-inngangen er koblet til R-inngangen. D-inngangen sendes videre til flip flop når verdien AV CP er ‘1’. Når CP ER HØY, flytter flip flop TIL SETTET tilstand. Hvis det er ‘0’, bytter flip flop TIL KLAR tilstand.

for å vite mer om utløsningen av flip flop klikk på linken nedenfor.

TA EN TITT : UTLØSING AV FLIP FLOPS

TA EN TITT: MASTER-SLAVE FLIP FLOP CIRCUIT

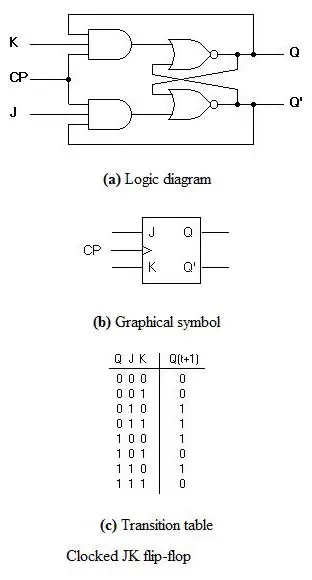

J-K Flip Flop

kretsdiagrammet og sannhetstabellen til En j-K flip flop er vist nedenfor.

En j-K flip flop kan også defineres som en modifikasjon Av S-R flip flop. Den eneste forskjellen er at mellomstaten er mer raffinert og presis enn En Sr-flip-flop.

oppførselen Til innganger J Og K er den samme som s og R innganger På S-R flip flop. Bokstaven J står FOR SET og bokstaven K står FOR CLEAR.

når både inngangene J Og K har EN HØY tilstand, bytter flip-flop til komplementtilstanden. Så, For en verdi På Q = 1, bytter Den Til Q = 0 og For en verdi På Q = 0, bytter Den Til Q=1.

kretsen inneholder to 3-inngang og porter. Utgang Q av flip flop returneres tilbake som en tilbakemelding til inngangen AV OG sammen med andre innganger Som K og klokke puls . Så, hvis verdien AV CP er ‘1’, får flip flop ET KLART signal og med betingelsen Om at verdien Av Q var tidligere 1. Tilsvarende utgang Q ‘ av flip flop er gitt som en tilbakemelding til input AV OG sammen med andre innganger Som J og klokke puls . Så utgangen BLIR SATT når verdien AV CP er 1 bare hvis verdien Av Q ‘ var tidligere 1.

utgangen kan gjentas i overganger når De har blitt komplimentert For J = K = 1 på grunn av tilbakemeldingsforbindelsen I jk flip-flop. Dette kan unngås ved å sette en tidsvarighet mindre enn forplantningsforsinkelsen gjennom flip-flop. Begrensningen på pulsbredden kan elimineres med en master-slave eller kantutløst konstruksjon.

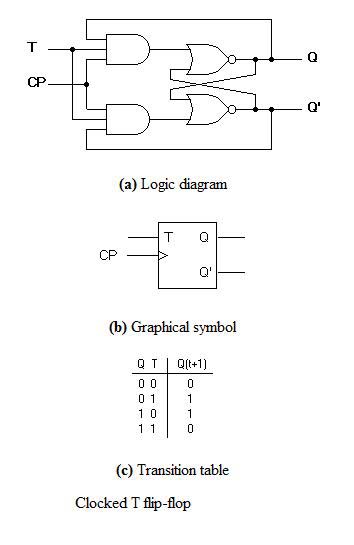

T Flip Flop

Dette er en mye enklere versjon Av jk flip flop. Både j Og K innganger er koblet sammen og dermed kalles også en enkelt inngang J-K flip flop. Når klokkepuls er gitt til flip flop, begynner utgangen å veksle. Her kan også begrensningen på pulsbredden elimineres med en master-slave eller kantutløst konstruksjon. Ta en titt på kretsen og sannheten tabellen nedenfor.