Flipflops in digitale elektronica

laten we in dit artikel leren over verschillende soorten teenslippers die worden gebruikt in digitale elektronica.

Basic Flip Flops in Digital Electronics

dit artikel behandelt de basic flip flop circuits zoals S-R Flip Flop, J-K Flip Flop, D Flip Flop, en T Flip flop samen met waarheidstabellen en de bijbehorende circuitsymbolen.

voordat u naar het onderwerp gaat is het belangrijk dat u kennis krijgt van de basis. Klik op de onderstaande links voor meer informatie.

kijk eens: Booleaanse logica

kijk eens : LOGIC GATES

kijk eens : halve ADDER en volledige ADDER

slippers zijn eigenlijk een toepassing van logic gates. Met behulp van Booleaanse logica kunt u geheugen creëren met hen. Slippers kunnen ook worden beschouwd als het meest fundamentele idee van een willekeurig toegangsgeheugen . Wanneer een bepaalde invoerwaarde aan hen wordt gegeven, zullen ze worden onthouden en uitgevoerd, als de logische poorten correct zijn ontworpen. Een hogere toepassing van teenslippers is nuttig bij het ontwerpen van betere elektronische circuits.

de meest gebruikte toepassing van teenslippers is de implementatie van een feedbackcircuit. Omdat een geheugen afhankelijk is van het feedback-concept, kunnen teenslippers worden gebruikt om het te ontwerpen.

er zijn hoofdzakelijk vier soorten teenslippers die in elektronische schakelingen worden gebruikt. Ze zijn

- de basis Flipflop of S-R Flipflop

- Delay Flipflop

- J-K Flipflop

- T Flipflop

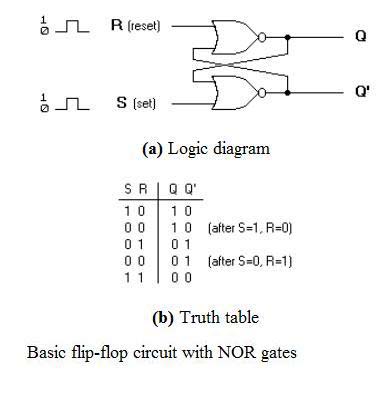

S-R Flipflop

de set-RESET flipflop is ontworpen met behulp van twee NOR-poorten en ook twee NAND-poorten. Deze teenslippers worden ook wel S-R Latch genoemd.

-

S-R Flip Flop met NOR Gate

het ontwerp van een dergelijke flip flop omvat twee ingangen, genaamd de SET en RESET . Er zijn ook twee uitgangen, Q en Q’. Het diagram en de waarheidstabel zijn hieronder weergegeven.

uit het diagram blijkt dat de flip flop voornamelijk vier toestanden heeft. Ze zijn

S = 1, R = 0-Q= 1, Q ‘ = 0

deze toestand wordt ook wel de ingestelde toestand genoemd.

S = 0, R = 1-Q = 0, Q ‘ = 1

deze toestand staat bekend als de RESETTOESTAND.

in beide toestanden kunt u zien dat de uitgangen alleen complimenten van elkaar zijn en dat de waarde van Q de waarde van S. volgt.

S = 0, R—0-Q & Q ‘ = Remember

als zowel de waarden van S als R worden overgeschakeld naar 0, dan onthoudt het circuit de waarde van S en R in hun vorige toestand.

S = 1, R—1-Q = 0, Q ‘= 0

dit is een ongeldige status omdat de waarden van zowel Q als Q ‘ 0 zijn. Ze horen complimenten van elkaar te zijn. Normaal gesproken moet deze toestand worden vermeden.

-

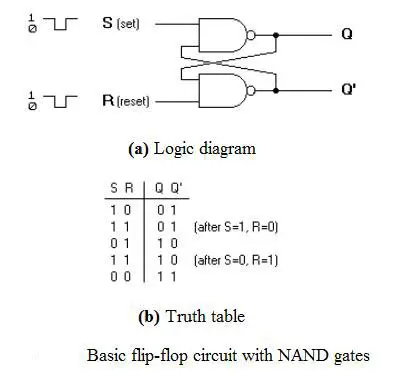

S-R Flip Flop met NAND Gate

het circuit van de S-R flip flop met behulp van NAND Gate en de waarheidstabel is hieronder weergegeven.

net als de Nor Gate S-R flip flop heeft deze ook vier toestanden. Ze zijn

S = 1, R = 0-Q=0, Q ‘ = 1

deze toestand wordt ook wel de ingestelde toestand genoemd.

S = 0, R = 1-Q = 1, Q ‘ = 0

deze toestand staat bekend als de RESETTOESTAND.

in beide toestanden kunt u zien dat de uitgangen gewoon complimenten van elkaar zijn en dat de waarde van Q de complimentwaarde van S. volgt.

S = 0, R—0-Q = 1, & Q ‘= 1

als beide waarden van S en R naar 0 worden overgeschakeld, is dit een ongeldige status omdat de waarden van zowel Q Als Q ‘ 1 zijn. Ze horen complimenten van elkaar te zijn. Normaal gesproken moet deze toestand worden vermeden.

S = 1, R = 1-Q & Q ‘ = Remember

als zowel de waarden van S als R worden geschakeld naar 1, dan onthoudt het circuit de waarde van S en R in hun vorige toestand.

-

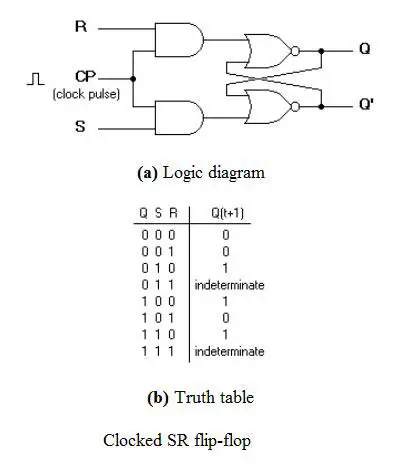

geklokte S-R teenslippers

het wordt ook wel een Gated s-R flip flop genoemd.

de problemen met S-R slippers die gebruik maken van NOR en NAND gate is de ongeldige status. Dit probleem kan worden opgelost met behulp van een bistable SR flip-flop die uitgangen kan veranderen wanneer aan bepaalde ongeldige toestanden wordt voldaan, ongeacht de conditie van de Set of de Reset-ingangen. Hiervoor is een geklokte s-R flip flop ontworpen door twee en poorten toe te voegen aan een basic nor Gate flip flop. Het schema en de waarheidstabel zijn hieronder weergegeven.

er wordt een klokpuls gegeven aan de ingangen van de poort. Wanneer de waarde van de klokpuls ‘0’ is, blijven de uitgangen van zowel de poort als de poort ‘0’. Zodra een puls wordt gegeven de waarde van CP draait ‘1’. Dit maakt de waarden op S en R door de nor Gate flip flop. Maar wanneer de waarden van zowel S als R ‘1’ draaien, zorgt de hoge waarde van CP ervoor dat beide even naar ‘0’ draaien. Zodra de puls is verwijderd, wordt de flip flop-toestand intermediair. Zo kan elk van de twee toestanden worden veroorzaakt, en het hangt af van of de set of reset input van de flip-flop een ‘1’ langer blijft dan de overgang naar’ 0 ‘ aan het einde van de puls. Zo kunnen de ongeldige toestanden worden geëlimineerd.

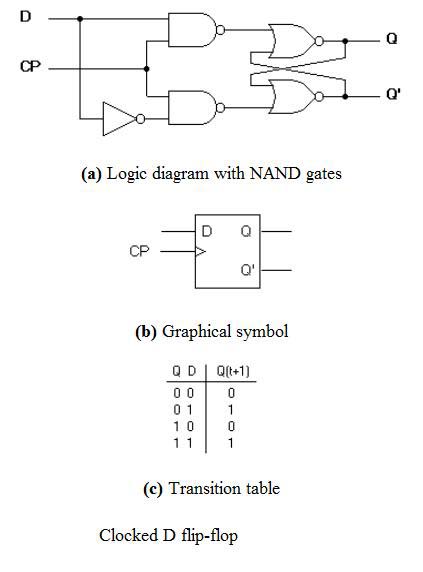

d Flipflop

het schema en de waarheidstabel zijn hieronder weergegeven.

D flip flop is eigenlijk een kleine wijziging van de hierboven beschreven geklokte SR flip-flop. Uit de figuur kunt u zien dat de D-ingang is aangesloten op de S-ingang en de aanvulling van de D-ingang is aangesloten op de R-ingang. De D input wordt doorgegeven aan de flip flop wanneer de waarde van CP ‘1’is. Als CP hoog is, gaat de flip flop naar de ingestelde status. Als het ‘0’ is, schakelt de flip flop over naar de CLEAR status.

om meer te weten te komen over de triggering van flip flop klik op de onderstaande link.

kijk : TRIGGERING van teenslippers

kijk : MASTER-SLAVE TEENSLIPPERCIRCUIT

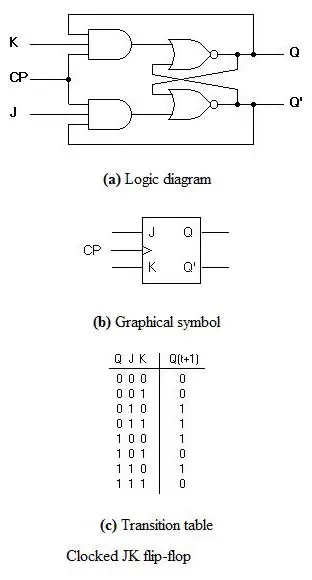

J-K Teenslippercircuit

het schema en de waarheidstabel van een J-K teenslippercircuit zijn hieronder weergegeven.

een J-K flip flop kan ook worden gedefinieerd als een wijziging van de S-R flip flop. Het enige verschil is dat de tussentoestand verfijnder en nauwkeuriger is dan die van een S-R flip flop.

het gedrag van ingangen J en K is hetzelfde als de s en R ingangen van de S-R flip flop. De letter J staat voor SET en de letter K staat voor CLEAR.

wanneer zowel de ingangen J als K een hoge status hebben, schakelt de flip-flop over naar de complementstatus. Dus, voor een waarde van Q = 1, schakelt het naar Q = 0 en voor een waarde van Q = 0, schakelt het naar Q=1.

het circuit bevat twee 3-ingangen en poorten. De uitgang Q van de flip flop wordt teruggestuurd als een terugkoppeling naar de ingang van de en samen met andere ingangen zoals K en klok puls . Dus, als de waarde van CP ‘1’ is, krijgt de flip flop een duidelijk signaal en met de voorwaarde dat de waarde van Q eerder 1 was. Op dezelfde manier wordt output Q’ van de flip flop gegeven als feedback aan de input van en samen met andere ingangen zoals J en klokpuls . Dus de output wordt ingesteld als de waarde van CP 1 is alleen als de waarde van Q ‘ eerder 1 was.

de output kan worden herhaald in overgangen nadat ze zijn gecomplimenteerd voor J = K = 1 vanwege de feedbackverbinding in de JK flip-flop. Dit kan worden vermeden door een tijdsduur in te stellen die kleiner is dan de voortplantingsvertraging door de flip-flop. De beperking van de pulsbreedte kan worden geëlimineerd met een master-slave of edge-triggered constructie.

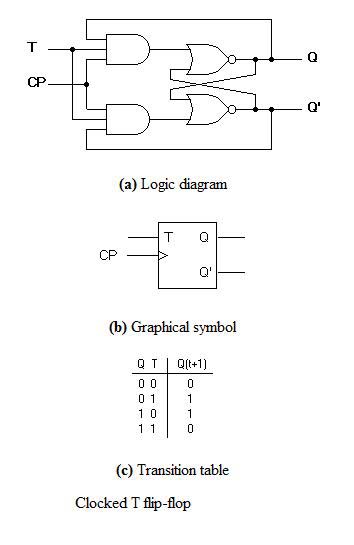

T Flip flop

Dit is een veel eenvoudiger versie van de J-K flip flop. Zowel de J-als K-ingangen zijn met elkaar verbonden en worden dus ook wel een single input J-K flip flop genoemd. Wanneer klokpuls aan de flip flop wordt gegeven, begint de output te schakelen. Ook hier kan de beperking van de pulsbreedte worden geëlimineerd met een master-slave of randgestuurde constructie. Neem een kijkje op de circuit en waarheid tabel hieronder.