Flip-Flops em Eletrônica Digital

neste artigo, vamos aprender sobre os diferentes tipos de flip-flops usados em eletrônica digital.

Chinelos básicos em electrónica Digital

este artigo trata dos circuitos básicos de flip flop como o S-R Flip Flop, J-K Flip Flop, D Flip Flop, e t Flip Flop juntamente com as tabelas de verdade e seus símbolos de circuito correspondentes.

Antes de ir para o tópico é importante que você tenha conhecimento de seus fundamentos. Clique nos links abaixo para mais informações.

dê UMA OLHADA : LÓGICA BOOLEANA

dê UMA OLHADA : PORTAS lógicas

dê UMA OLHADA : MEIO SOMADOR E SOMADOR COMPLETO

Flip-flops são, na verdade, um aplicativo de portas lógicas. Com a ajuda da lógica booleana você pode criar memória com eles. Chinelos também podem ser considerados como a idéia mais básica de uma memória de acesso aleatório . Quando um determinado valor de entrada é dado a eles, eles serão lembrados e executados, se as portas lógicas são projetadas corretamente. Uma aplicação mais elevada de chinelos é útil na concepção de circuitos electrónicos melhores.

a aplicação mais comumente usada de chinelos está na implementação de um circuito de feedback. Como uma memória depende do conceito de feedback, chinelos podem ser usados para projetá-lo.

existem principalmente quatro tipos de flip flops que são usados em circuitos eletrônicos. Eles são

S-R Flip Flop

SET-RESET flip-flop é projetado com a ajuda de dois NEM portas e também duas portas NAND. Estes chinelos também são chamados de trinco S-R.

-

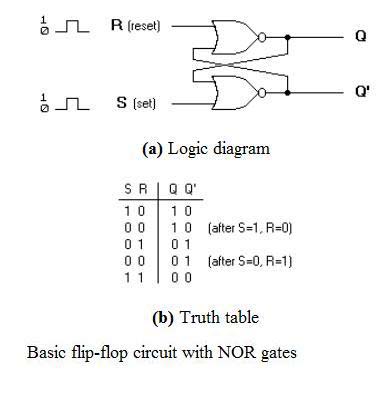

Flip Flop S-R usando o NOR Gate

o design de tal flip flop inclui duas entradas, chamadas de SET e RESET . Há também duas saídas, Q e Q’. O diagrama e a tabela verdade são mostrados abaixo.

a partir do diagrama é evidente que o flip flop tem principalmente quatro estados. Eles são

S = 1, R=0—Q=1, Q’=0

este estado também é chamado de Estado conjunto.

S = 0, R = 1-Q=0, Q’=1

este estado é conhecido como o estado de RESET.

em ambos os estados você pode ver que as saídas são apenas cumprimentos um do outro e que o valor de Q segue o valor de S.

S = 0, R = 0-Q & Q ‘ = recordar

se ambos os valores de S e R forem mudados para 0, então o circuito recorda o valor de s e R no seu estado anterior.

S = 1, R=1—Q=0, Q’=0

este é um estado inválido porque os valores de Q e Q’ São 0. É suposto serem cumprimentos um do outro. Normalmente, este estado deve ser evitado.

-

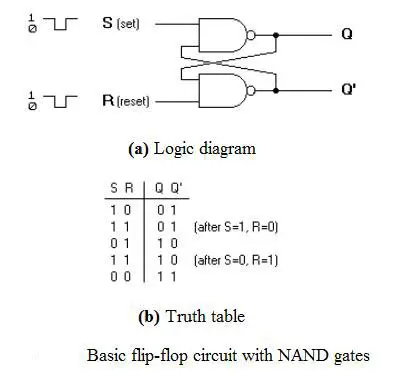

Flip Flop S-R com porta NAND

o circuito do flip flop S-R usando Nand Gate e sua tabela de verdade é mostrado abaixo.

como a porta NOR S-R flip flop, esta também tem quatro estados. Eles são

S = 1, R=0—Q=0, Q’=1

este estado também é chamado de Estado conjunto.

S = 0, R = 1-Q=1, Q’=0

este estado é conhecido como o estado de RESET.

em ambos os estados você pode ver que as saídas são apenas cumprimentos um do outro e que o valor de Q segue o valor de elogio de S.

S=0, R=0 Q=1, & Q’ =1

Se ambos os valores de S e R são comutadas para 0 é um estado inválido porque os valores de Q e Q’ são 1. É suposto serem cumprimentos um do outro. Normalmente, este estado deve ser evitado.

S = 1, R=1—Q & Q’= lembre-se

se ambos os valores de S e R forem mudados para 1, Então o circuito lembra o valor de s e R em seu estado anterior.

-

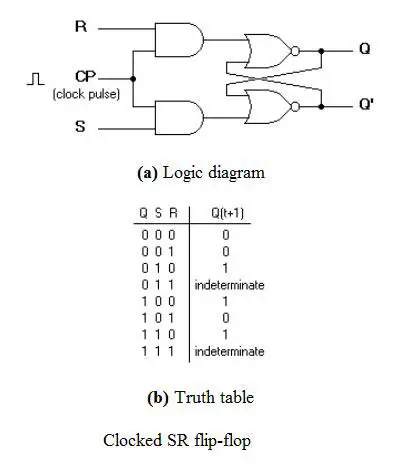

Flip Flop S-R Com Fecho

também é chamado de Patado S-R flip flop.

os problemas com os chinelos S-R usando NOR e NAND gate é o estado inválido. Este problema pode ser superado usando um flip-flop de SR bistable que pode alterar as saídas quando certos estados inválidos são cumpridos, independentemente da condição do conjunto ou as entradas de Reset. Para isso, um flip flop S-R é projetado adicionando dois e portões para um flip flop básico da NOR Gate. O diagrama do circuito e a tabela da verdade é mostrada abaixo.

um pulso de clock é dado às entradas do AND Gate. Quando o valor do pulso de clock é “0”, as saídas tanto das portas como das portas permanecem “0”. Assim que um pulso é dado o valor de CP gira ‘1’. Isto faz com que os valores em S E R passem pelo flip flop da porta NOR. Mas quando os valores de S e R se transformam em ‘1’, o alto valor de CP faz com que ambos se voltem para ‘0’ por um curto momento. Assim que o pulso é removido, o estado flip flop torna-se intermediário. Assim, qualquer um dos dois estados pode ser causado, e depende se o conjunto ou reset de entrada do flip-flop permanece um ‘1’ mais longo do que a transição para ‘0’ no final do pulso. Assim, os Estados inválidos podem ser eliminados.

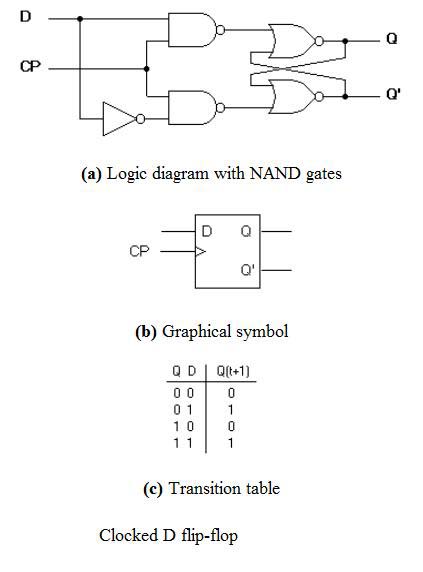

D Flip Flop

o diagrama do circuito e a tabela da verdade são apresentados abaixo.

D flip-flop é, na verdade, uma ligeira modificação do acima explicado clock SR flip-flop. A partir da figura você pode ver que a entrada D está conectada à entrada S e o complemento da entrada D está conectado à entrada R. A entrada D é passada para o flip flop quando o valor de CP é ‘1’. Quando o CP é alto, o flip flop move-se para o estado definido. Se for ‘0’ , o flip flop muda para o estado livre.

para saber mais sobre o desencadeamento do flip flop clique no link abaixo.

dê uma olhada : TRIGGERING OF FLIP flop

dê uma olhada : MASTER-SLAVE FLIP CIRCUIT

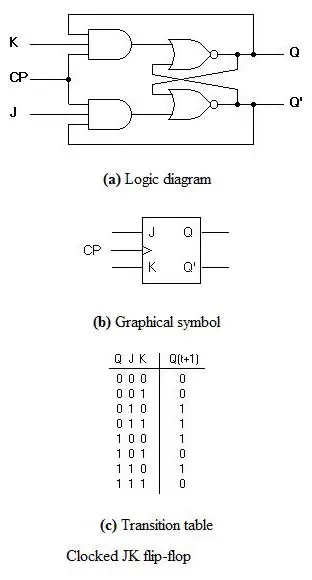

J-K Flip Flop

o diagrama do circuito e a tabela de verdade de um flip flop J-K é mostrado abaixo.

um flip flop J-K também pode ser definido como uma modificação do flip flop S-R. A única diferença é que o estado intermediário é mais refinado e preciso do que o de um flip flop S-R.

o comportamento das entradas J E K é o mesmo que as entradas S E R do flip flop S-R. A letra J significa SET e a letra K significa CLEAR.

quando ambas as entradas J E K têm um estado elevado, o flip-flop muda para o estado do complemento. Então, para um valor de Q = 1, ele muda para Q=0 e para um valor de Q = 0, ele muda para Q=1.

o circuito inclui duas portas e três entradas. A saída Q do flip flop é devolvida de volta como um feedback para a entrada do E junto com outras entradas como K e pulso de clock . Então, se o valor de CP é ‘1’, o flip flop recebe um sinal claro e com a condição de que o valor de Q era anterior 1. Similarmente a saída Q’ do flip flop é dada como um feedback para a entrada do E junto com outras entradas como o pulso de J E clock . Então a saída torna-se definida quando o valor de CP é 1 somente se o valor de Q’ era 1 anterior.

a saída pode ser repetida em transições uma vez que eles tenham sido elogiados para J=K=1 por causa da conexão de feedback no flip-flop JK. Isto pode ser evitado definindo uma duração de tempo menor do que o atraso de propagação através do flip-flop. A restrição da largura do pulso pode ser eliminada com uma construção master-slave ou edge-triggered.

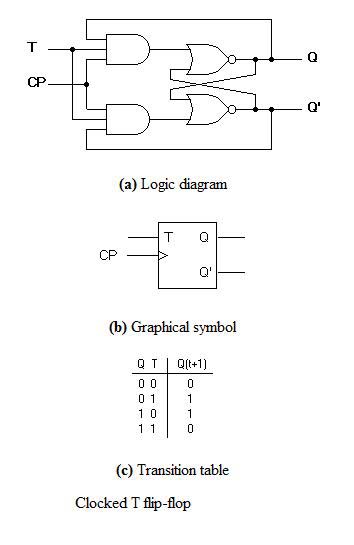

t Flip Flop

esta é uma versão muito mais simples do flip flop J-K. Ambas as entradas J E K são conectadas juntas e, portanto, também são chamadas de um único flip J-K de entrada. Quando o pulso de relógio é dado ao flip flop, a saída começa a comutar. Aqui também a restrição da largura do pulso pode ser eliminada com uma construção master-slave ou edge-triggered. Dê uma olhada na tabela de circuito e verdade abaixo.