Flip flops în electronică digitală

în acest articol, să învățăm despre diferite tipuri de flip flops utilizate în electronica digitală.

Basic Flip Flops in Digital Electronics

acest articol se ocupă cu circuite de bază flip flop ca S-R Flip Flop, J-K Flip flop, D Flip Flop, și T Flip Flop împreună cu tabele de adevăr și simbolurile lor de circuit corespunzătoare.

înainte de a merge la subiect, este important să obțineți cunoștințe despre elementele sale de bază. Faceți clic pe linkurile de mai jos pentru mai multe informații.

aruncați o privire : logica booleană

aruncați o privire : porțile logice

aruncați o privire : jumătate viperă și viperă completă

Flip flops sunt de fapt o aplicație a porților logice. Cu ajutorul logicii booleene puteți crea memorie cu ei. Flip flops poate fi, de asemenea, considerată ca fiind cea mai de bază idee a unei memorii cu acces aleatoriu . Când li se dă o anumită valoare de intrare, acestea vor fi amintite și executate, Dacă porțile logice sunt proiectate corect. O aplicație mai mare de flip flops este utilă în proiectarea circuitelor electronice mai bune.

cea mai frecvent utilizată aplicație de flip flops este în implementarea unui circuit de feedback. Deoarece o memorie se bazează pe conceptul de feedback, flip flops pot fi folosite pentru a-l proiecta.

există în principal patru tipuri de flip flops care sunt utilizate în circuitele electronice. Acestea sunt

- Basic Flip Flop sau S-R Flip Flop

- întârziere Flip Flop

- J-K Flip Flop

- t Flip flop

S-R Flip Flop

set-RESET flip flop este proiectat cu ajutorul a două porți NOR și, de asemenea, două porți NAND. Aceste flip flops sunt, de asemenea, numite zăvor S-R.

-

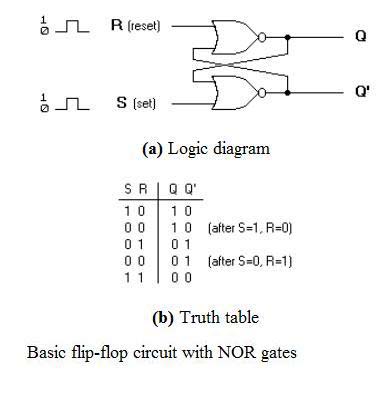

S – R Flip Flop folosind poarta NOR

designul unui astfel de flip flop include două intrări, numite SET și resetare . Există, de asemenea, două ieșiri, Q și Q’. Diagrama și tabelul adevărului sunt prezentate mai jos.

din diagramă este evident că flip flop-ul are în principal patru stări. Ele sunt

S=1, R=0—Q=1, Q’=0

această stare este numită și starea setată.

S=0, R=1—Q=0, Q’=1

această stare este cunoscută ca starea de resetare.

în ambele stări puteți vedea că ieșirile sunt doar complimente unul față de celălalt și că valoarea lui Q urmează valoarea lui S.

S=0, R=0—Q & Q’ = amintiți-vă

dacă ambele valori ale lui S și R sunt comutate la 0, atunci circuitul își amintește valoarea lui s și R în starea lor anterioară.

S=1, R=1—Q=0, Q’=0

aceasta este o stare nevalidă deoarece valorile lui Q și Q’ sunt 0. Ar trebui să fie complimente unul de celălalt. În mod normal, această stare trebuie evitată.

-

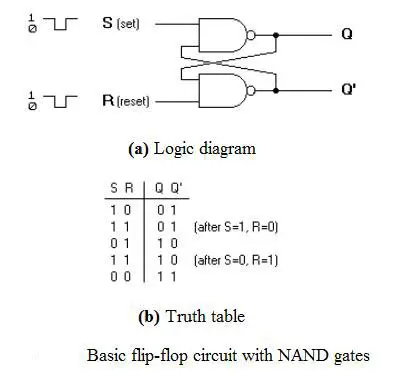

S-R Flip Flop folosind poarta NAND

circuitul flip flop-ului S-R folosind poarta NAND și tabelul său de adevăr este prezentat mai jos.

ca și poarta NOR s-r flip flop, aceasta are și patru stări. Ele sunt

S=1, R=0—Q=0, Q’=1

această stare este numită și starea setată.

S=0, R=1—Q=1, Q’=0

această stare este cunoscută ca starea de resetare.

în ambele stări puteți vedea că rezultatele sunt doar complimente unul față de celălalt și că valoarea lui Q urmează valoarea complimentului lui S.

S=0, R=0—Q=1, & Q’ =1

dacă ambele valori ale lui S și R sunt comutate la 0, este o stare nevalidă deoarece valorile lui Q și Q’ sunt 1. Ar trebui să fie complimente unul de celălalt. În mod normal, această stare trebuie evitată.

S=1, R=1—Q & Q’= amintiți-vă

dacă ambele valori ale lui S și R sunt comutate la 1, atunci circuitul își amintește valoarea lui s și R în starea lor anterioară.

-

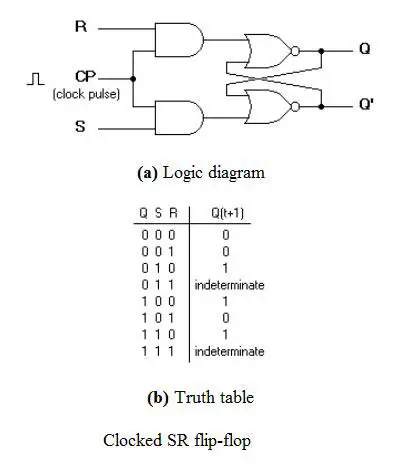

ceas S-R Flip Flop

se mai numește și un flip flop S-R închis.

problemele cu S-R flip flops folosind NOR și NAND gate este starea nevalidă. Această problemă poate fi depășită prin utilizarea unui flip-flop SR bistabil care poate schimba ieșirile atunci când sunt îndeplinite anumite stări nevalide, indiferent de starea fie a intrărilor setate, fie a celor resetate. Pentru aceasta, un flip flop s-r tactat este proiectat prin adăugarea a două și porți la un flip flop de bază NOR Gate. Diagrama circuitului și tabelul adevărului sunt prezentate mai jos.

un impuls de ceas este dat la intrările porții și. Când valoarea impulsului ceasului este ‘0’, ieșirile ambelor porți și ale porților rămân’0′. De îndată ce un impuls este dat valoarea CP se transformă ‘1’. Acest lucru face ca valorile de la S și R să treacă prin poarta nor flip flop. Dar când valorile ambelor valori S și R se transformă în ‘1’, valoarea ridicată a CP face ca ambele să se întoarcă la ‘0’ pentru un moment scurt. De îndată ce pulsul este îndepărtat, starea flip flop devine intermediară. Astfel, oricare dintre cele două stări poate fi cauzată și depinde dacă intrarea setată sau resetată a flip-flop-ului rămâne cu ‘1’ mai lungă decât trecerea la ‘0’ la sfârșitul impulsului. Astfel, stările nevalide pot fi eliminate.

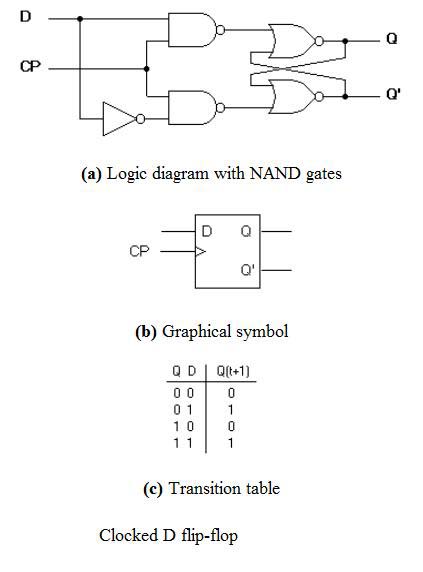

D Flip Flop

diagrama circuitului și tabelul adevărului sunt prezentate mai jos.

D flip flop este de fapt o ușoară modificare a explicat mai sus tactat SR flip-flop. Din figură puteți vedea că intrarea D este conectată la intrarea S și complementul intrării D este conectat la intrarea R. Intrarea D este transmisă pe flip flop atunci când valoarea CP este ‘1’. Când CP este mare, flip flop se mută la starea setată. Dacă este ‘0’, flip flop-ul trece la starea clară.

pentru a afla mai multe despre declanșarea flip flop click pe link-ul de mai jos.

aruncați o privire : declanșarea FLIP-flop-urilor

aruncați o privire : circuitul FLIP-flop MASTER-SLAVE

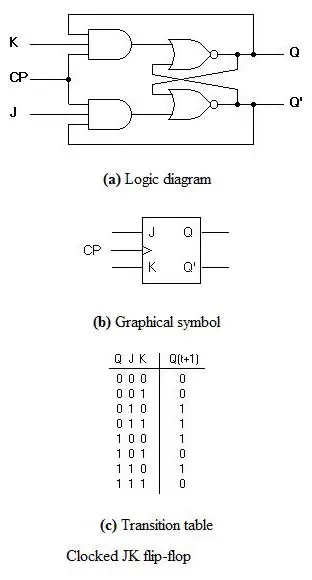

Flip-Flop J-K

diagrama circuitului și tabelul de adevăr al unui flip-flop J-K sunt prezentate mai jos.

un flip flop J-K poate fi, de asemenea, definit ca o modificare a flip flop-ului S-R. Singura diferență este că starea intermediară este mai rafinată și mai precisă decât cea a unui flip flop S-R.

comportamentul intrărilor J și K este același cu intrările S și R ale flip flop-ului S-R. Litera J înseamnă SET și litera K înseamnă clar.

când ambele intrări J și K au o stare ridicată, flip-flop-ul trece la starea complementului. Deci, pentru o valoare de Q = 1, trece la Q=0 și pentru o valoare de Q = 0, trece la Q=1.

circuitul include două intrări 3 și porți. Ieșirea Q A flip flop-ului este returnată înapoi ca feedback la intrarea și împreună cu alte intrări, cum ar fi K și pulsul ceasului . Deci, dacă valoarea CP este ‘1’, flip flop-ul primește un semnal clar și cu condiția ca valoarea Q să fie mai devreme 1. În mod similar, ieșirea Q’ A flip flop-ului este dată ca feedback la intrarea și împreună cu alte intrări, cum ar fi J și pulsul ceasului . Deci, ieșirea devine setată atunci când valoarea CP este 1 numai dacă valoarea Q’ A fost mai devreme 1.

ieșirea poate fi repetată în tranziții odată ce au fost complimentate pentru J=K=1 din cauza conexiunii de feedback din flip-flop-ul JK. Acest lucru poate fi evitat prin setarea unei durate de timp mai mică decât întârzierea propagării prin flip-flop. Restricția privind lățimea impulsului poate fi eliminată cu o construcție master-slave sau declanșată de margine.

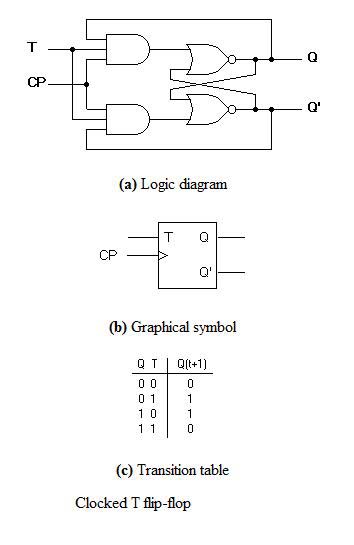

t Flip Flop

aceasta este o versiune mult mai simplă A J-K flip flop. Ambele intrări J și K sunt conectate împreună și, prin urmare, sunt numite și o singură intrare J-K flip flop. Când pulsul ceasului este dat la flip flop, ieșirea începe să comute. Aici, de asemenea, restricția privind lățimea impulsului poate fi eliminată cu o construcție master-slave sau declanșată de margine. Aruncați o privire la tabelul circuit și adevăr de mai jos.