Flip Flops i Digital elektronik

i den här artikeln lär vi oss om olika typer av flip-flops som används i digital elektronik.

grundläggande Flip Flops i Digital elektronik

den här artikeln behandlar de grundläggande flip flop-kretsarna som S-R Flip Flop, J-K Flip Flop, D Flip Flop och T Flip Flop tillsammans med sanningstabeller och deras motsvarande kretssymboler.

innan du går till ämnet är det viktigt att du får kunskap om dess grunder. Klicka på länkarna nedan för mer information.

ta en titt: boolesk logik

ta en titt : logiska grindar

ta en titt : halv ADDER och FULL ADDER

Flip flops är faktiskt en tillämpning av logiska grindar. Med hjälp av boolesk logik kan du skapa minne med dem. Flip flops kan också betraktas som den mest grundläggande tanken på ett slumpmässigt åtkomstminne . När ett visst ingångsvärde ges till dem kommer de att komma ihåg och exekveras om de logiska grindarna är utformade korrekt. En högre tillämpning av flip flops är till hjälp vid utformning av bättre elektroniska kretsar.

den vanligaste tillämpningen av flip flops är i genomförandet av en återkopplingskrets. Eftersom ett minne bygger på feedbackkonceptet kan flip-flops användas för att designa det.

det finns huvudsakligen fyra typer av flip-flops som används i elektroniska kretsar. De är

- den grundläggande Flip Flop eller S-R Flip Flop

- Delay Flip Flop

- J-K Flip Flop

- t Flip Flop

S-r Flip Flop

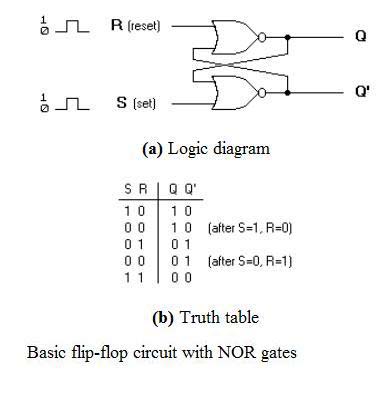

set-RESET flip flop är utformad för med hjälp av två NOR-grindar och även två NAND-grindar. Dessa flip flops kallas också S – R Latch.

-

s-r Flip Flop använder NOR Gate

utformningen av en sådan flip flop innehåller två ingångar, kallad SET och RESET . Det finns också två utgångar, Q och Q’. Diagrammet och sanningstabellen visas nedan.

från diagrammet är det uppenbart att flip flop har huvudsakligen fyra stater. De är

S=1, R=0—Q=1, Q’=0

detta tillstånd kallas också det inställda tillståndet.

S = 0, R=1—Q=0, Q’=1

detta tillstånd kallas ÅTERSTÄLLNINGSTILLSTÅNDET.

i båda staterna kan du se att utgångarna bara är komplimanger av varandra och att värdet på Q följer värdet på S.

S = 0, R=0—Q & Q’ = kom ihåg

om både värdena på S och R byts till 0, kommer kretsen ihåg värdet på S och R i sitt tidigare tillstånd.

S=1, R=1—Q=0, Q’=0

detta är ett ogiltigt tillstånd eftersom värdena för både Q och Q’ är 0. De ska vara komplimanger av varandra. Normalt måste detta tillstånd undvikas.

-

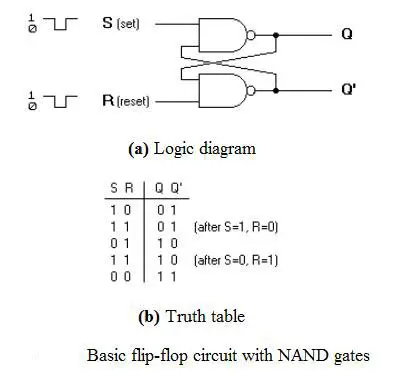

s-r Flip Flop använder NAND Gate

kretsen av s-r flip flop använder NAND Gate och dess sanning tabellen visas nedan.

liksom NOR Gate s-r flip flop har den här också fyra tillstånd. De är

S=1, R=0—Q=0, Q’=1

detta tillstånd kallas också det inställda tillståndet.

S = 0, R=1—Q=1, Q’=0

detta tillstånd kallas ÅTERSTÄLLNINGSTILLSTÅNDET.

i båda staterna kan du se att utgångarna bara är komplimanger av varandra och att värdet på Q följer komplimangvärdet för S.

S = 0, R=0—Q=1, & Q’ =1

om båda värdena för S och R byts till 0 är det ett ogiltigt tillstånd eftersom värdena för både Q och Q’ är 1. De ska vara komplimanger av varandra. Normalt måste detta tillstånd undvikas.

S=1, R=1—Q & Q’= kom ihåg

om både värdena på S och R byts till 1, kommer kretsen ihåg värdet på S och R i sitt tidigare tillstånd.

-

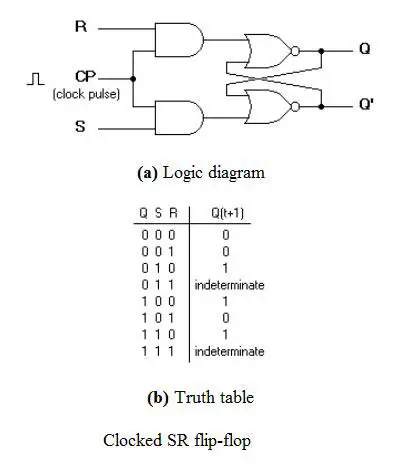

klockad s-r Flip Flop

det kallas också en Gated s-r flip flop.

problemen med s-r flip flops använder NOR och NAND gate är ogiltigt tillstånd. Detta problem kan övervinnas genom att använda en bistabil SR-flip-flop som kan ändra utgångar när vissa ogiltiga tillstånd är uppfyllda, oavsett villkoret för antingen Set-eller Reset-ingångarna. För detta är en klockad s-r flip flop utformad genom att lägga till två och grindar till en grundläggande nor Gate flip flop. Kretsschemat och sanningstabellen visas nedan.

en klockpuls ges till ingångarna i och Gate. När värdet på klockpulsen är ’ 0 ’förblir utgångarna från både grindarna och grindarna’0’. Så snart en puls ges värdet av CP blir ’1’. Detta gör att värdena vid S och R passerar genom nor Gate flip flop. Men när värdena för både S-och R-värden blir ’1’, får det höga värdet av CP båda att vända sig till ’0’ för ett kort ögonblick. Så snart pulsen avlägsnas blir flip flop-tillståndet mellanliggande. Således kan någon av de två tillstånden orsakas, och det beror på om den inställda eller återställda ingången på flip-flop förblir en ’1’ längre än övergången till ’0’ i slutet av pulsen. Således kan de ogiltiga tillstånden elimineras.

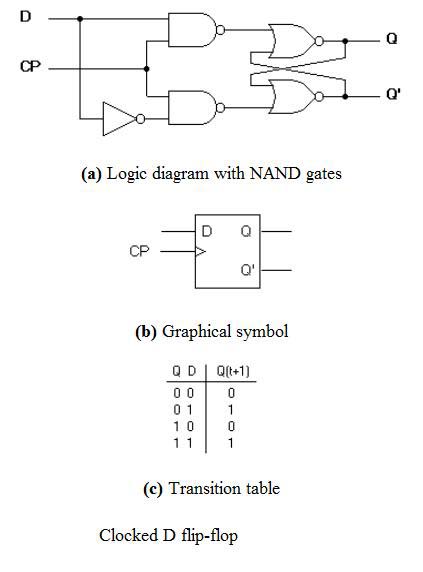

D Flip Flop

kretsschemat och sanningstabellen ges nedan.

D flip flop är faktiskt en liten modifiering av ovanstående förklarade klockade SR flip-flop. Från figuren kan du se att d-ingången är ansluten till s-ingången och komplementet till D-ingången är ansluten till R-ingången. D-ingången överförs till flip flop när värdet på CP är ’1’. När CP är hög flyttas flip flop till inställt tillstånd. Om det är ’0’, växlar flip flop till klart tillstånd.

för att veta mer om utlösningen av flip flop klicka på länken nedan.

ta en titt: utlösning av FLIP FLOPS

ta en titt: MASTER-SLAVE FLIP FLOP CIRCUIT

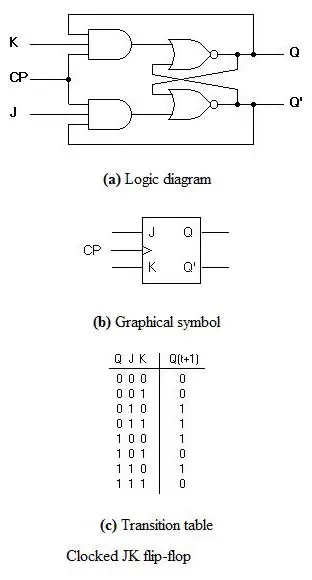

J-K Flip Flop

kretsschemat och sanningstabellen för en J-K flip flop visas nedan.

en J-K flip flop kan också definieras som en modifiering av S-R flip flop. Den enda skillnaden är att mellantillståndet är mer raffinerat och exakt än för en s-r flip flop.

beteendet hos ingångarna J och K är samma som s-och R-ingångarna på s-r flip flop. Bokstaven J står för SET och bokstaven K står för CLEAR.

när båda ingångarna J och K har ett högt tillstånd växlar flip-flop till komplementtillståndet. Så för ett värde på Q = 1 växlar det till Q=0 och för ett värde på Q = 0 växlar det till Q=1.

kretsen innehåller två 3-ingångar och grindar. Utgången Q på flip flop returneras tillbaka som en återkoppling till ingången på och tillsammans med andra ingångar som K och klockpuls . Så, om värdet på CP är ’1’, får flip flop en tydlig signal och med villkoret att värdet på Q var tidigare 1. Liknande Utgång Q ’ av flip flop ges som en återkoppling till ingången av och tillsammans med andra ingångar som J och klockpuls . Så utgången blir inställd när värdet på CP är 1 endast om värdet på Q’ var tidigare 1.

utgången kan upprepas i övergångar när de har kompletterats för J = K = 1 på grund av återkopplingsanslutningen i JK-flip-flop. Detta kan undvikas genom att ställa in en tidslängd som är mindre än förökningsfördröjningen genom flip-flop. Begränsningen av pulsbredden kan elimineras med en master-slav eller kantutlöst konstruktion.

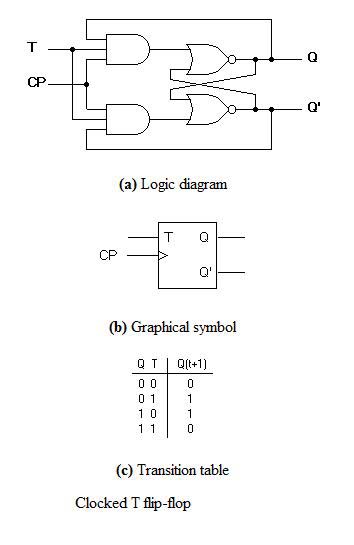

t Flip Flop

Detta är en mycket enklare version av JK flip flop. Både J-och K-ingångarna är anslutna ihop och kallas således också en enda ingång J-K flip flop. När klockpuls ges till flip flop, utgången börjar växla. Här kan också begränsningen av pulsbredden elimineras med en master-slav eller kantutlöst konstruktion. Ta en titt på kretsen och sanningstabellen nedan.